### **W&M ScholarWorks**

Dissertations, Theses, and Masters Projects

Theses, Dissertations, & Master Projects

2019

# GPGPU Reliability Analysis: From Applications to Large Scale **Systems**

Bin Nie William & Mary - Arts & Sciences, bnie0307@gmail.com

Follow this and additional works at: https://scholarworks.wm.edu/etd

Part of the Computer Sciences Commons

#### **Recommended Citation**

Nie, Bin, "GPGPU Reliability Analysis: From Applications to Large Scale Systems" (2019). Dissertations, Theses, and Masters Projects. William & Mary. Paper 1563898932. http://dx.doi.org/10.21220/s2-j086-2347

This Dissertation is brought to you for free and open access by the Theses, Dissertations, & Master Projects at W&M ScholarWorks. It has been accepted for inclusion in Dissertations, Theses, and Masters Projects by an authorized administrator of W&M ScholarWorks. For more information, please contact scholarworks@wm.edu.

# GPGPU Reliability Analysis: from Applications to Large Scale Systems

#### Bin Nie

Dalian, Liaoning, China

Master of Science, Fordham University, 2014 Bachelor of Engineer, Xiamen University, 2012

A Dissertation presented to the Graduate Faculty of The College of William & Mary in Candidacy for the Degree of Doctor of Philosophy

Department of Computer Science

College of William & Mary May, 2019

#### APPROVAL PAGE

This Dissertation is submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Bin Nie ·

Approved by the Committee, May 2019

Committee Chair Professor Evgenia Smirni, Computer Science College of William & Mary

Professor Adwait Jog, Computer Science College of William & Mary

Professor Xu Liu, Computer Science College of William & Mary

Professor Bin Ren, Computer Science College of William & Mary

Professor Karthik Pattabiraman, Electrical and Computer Engineering University of British Columbia

#### ABSTRACT

Over the past decade, GPUs have become an integral part of mainstream high-performance computing (HPC) facilities. Since applications running on HPC systems are usually long-running, any error or failure could result in significant loss in scientific productivity and system resources. Even worse, since HPC systems face severe resilience challenges as progressing towards exascale computing, it is imperative to develop a better understanding of the reliability of GPUs. This dissertation fills this gap by providing an understanding of the effects of soft errors on the entire system and on specific applications.

To understand system-level reliability, a large-scale study on GPU soft errors in the field is conducted. The occurrences of GPU soft errors are linked to several temporal and spatial features, such as specific workloads, node location, temperature, and power consumption. Further, machine learning models are proposed to predict error occurrences on GPU nodes so as to proactively and dynamically turning on/off the costly error protection mechanisms based on prediction results.

To understand the effects of soft errors at the application level, an effective fault-injection framework is designed aiming to understand the reliability and resilience characteristics of GPGPU applications. This framework is effective in terms of reducing the tremendous number of fault injection locations to a manageable size while still preserving remarkable accuracy. This framework is validated with both single-bit and multi-bit fault models for various GPGPU benchmarks. Lastly, taking advantage of the proposed fault-injection framework, this dissertation develops a hierarchical approach to understanding the error resilience characteristics of GPGPU applications at kernel, CTA, and warp levels. In addition, given that some corrupted application outputs due to soft errors may be acceptable, we present a use case to show how to enable low-overhead yet reliable GPU computing for GPGPU applications.

## TABLE OF CONTENTS

| A  | cknow   | rledgme | nts                                               | vii  |

|----|---------|---------|---------------------------------------------------|------|

| De | edicat  | ion     |                                                   | viii |

| Li | st of   | Tables  |                                                   | ix   |

| Li | st of I | Figures |                                                   | xi   |

| 1  | Intro   | oductio | n                                                 | 1    |

|    | 1.1     | Contr   | ibutions                                          | 5    |

|    |         | 1.1.1   | GPU Reliability Analysis at the System Level      | 6    |

|    |         | 1.1.2   | GPU Reliability Analysis at the Application Level | 7    |

|    | 1.2     | Organ   | ization                                           | 8    |

| 2  | Back    | kground | d and Related Work                                | 9    |

|    | 2.1     | Benefi  | its of Accelerators on Large-Scale Systems        | 9    |

|    | 2.2     | Gener   | al-Purpose GPUs for Scientific Computing          | 11   |

|    |         | 2.2.1   | Baseline GPU Architecture                         | 12   |

|    |         | 2.2.2   | GPGPU Applications and Execution Model            | 13   |

|    |         | 2.2.3   | GPU Errors in the Field                           | 13   |

|    | 2.3     | Reliab  | oility Analysis in the Field                      | 14   |

|    |         | 2.3.1   | System-Level Reliability Analysis                 | 15   |

|    |         | 2.3.2   | Application-Level Reliability Analysis            | 17   |

|    | 2.4     | Chapt   | er Summary                                        | 18   |

| 3 | A L  | arge-Scale Study of Soft-Errors on GPUs in the Field            | 19 |

|---|------|-----------------------------------------------------------------|----|

|   | 3.1  | Related Work                                                    | 20 |

|   | 3.2  | Methodology                                                     | 22 |

|   |      | 3.2.1 Titan Supercomputer Organization and NVIDIA K20X GPU      |    |

|   |      | Architecture                                                    | 22 |

|   |      | 3.2.2 GPU Errors: Collection and Analysis Methodology           | 24 |

|   |      | 3.2.3 Limitations and Scope                                     | 25 |

|   | 3.3  | Analyzing Single Bit Errors (SBEs)                              | 26 |

|   | 3.4  | Analyzing Dynamic Page Retirement (DPR) Errors on the Titan Su- |    |

|   |      | percomputer                                                     | 33 |

|   | 3.5  | Analyzing Performance Variance in SBE and DPR Affected GPU      |    |

|   |      | Nodes                                                           | 38 |

|   | 3.6  | Effect of Temperature on Dynamic Page Retirement Errors         | 40 |

|   | 3.7  | Chapter Summary                                                 | 46 |

| 4 | Cha  | racterization of Single-Bit Error in the Wild                   | 47 |

|   | 4.1  | Temperature Characteristics                                     | 49 |

|   | 4.2  | GPU Error Characterization                                      | 53 |

|   |      | 4.2.1 SBE Offender Nodes                                        | 53 |

|   |      | 4.2.2 Application                                               | 54 |

|   |      | 4.2.3 Temperature and Power Consumption                         | 55 |

|   |      | 4.2.3.1 A bird's eye view                                       | 56 |

|   |      | 4.2.3.2 Considering the time dimension                          | 57 |

|   |      | 4.2.3.3 Considering the space dimension                         | 60 |

|   | 4.3  | Chapter Summary                                                 | 61 |

| 5 | Prec | licting GPU Soft-Errors with Neural Networks                    | 63 |

|   | 5.1  | Related Work                                                    | 65 |

|   |      | 5.1.1   | Applications of Machine Learning Models in Systems        | 65 |

|---|------|---------|-----------------------------------------------------------|----|

|   |      | 5.1.2   | Time Series Prediction                                    | 66 |

|   | 5.2  | Overv   | iew of the Methodology                                    | 66 |

|   | 5.3  | SBE F   | Prediction Framework                                      | 69 |

|   |      | 5.3.1   | Feature Selection                                         | 69 |

|   |      | 5.3.2   | Challenge: Imbalanced Data Set                            | 70 |

|   |      | 5.3.3   | Model Selection                                           | 73 |

|   | 5.4  | Evalua  | ation                                                     | 73 |

|   |      | 5.4.1   | Evaluation with Oracle Data                               | 74 |

|   |      | 5.4.2   | PRACTISE for Feature Prediction                           | 77 |

|   |      | 5.4.3   | SBE Prediction with PRACTISE                              | 78 |

|   | 5.5  | Discus  | ssion                                                     | 80 |

|   |      | 5.5.1   | Application of SBE Prediction                             | 80 |

|   |      | 5.5.2   | Open Problems and Challenges                              | 81 |

|   | 5.6  | Chapt   | er Summary                                                | 81 |

| 6 | Pred | licting | GPU Soft-Errors with a Variety of Machine Learning Models | 83 |

|   | 6.1  | Featur  | re Selection                                              | 84 |

|   |      | 6.1.1   | Temporal Features                                         | 84 |

|   |      | 6.1.2   | Spatial Features                                          | 85 |

|   | 6.2  | Machi   | ne Learning Framework and Model                           | 86 |

|   |      | 6.2.1   | Overview                                                  | 86 |

|   |      | 6.2.2   | Challenge: Imbalanced Dataset                             | 87 |

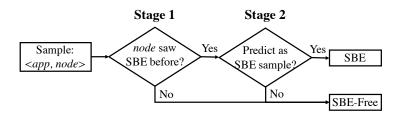

|   |      | 6.2.3   | Two-Stage Machine Learning Models                         | 88 |

|   |      | 6.2.4   | Machine Learning Model Selection                          | 90 |

|   | 6.3  | Evalua  | ation and Analysis                                        | 91 |

|   |      | 6.3.1   | Data Description and Evaluation Metrics                   | 91 |

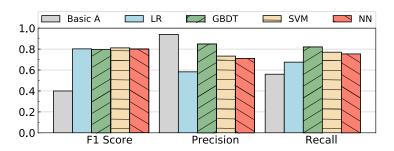

|   |      | 6.3.2    | Machine Learning Model Comparison                                   |

|---|------|----------|---------------------------------------------------------------------|

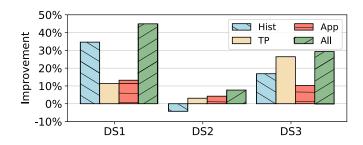

|   |      | 6.3.3    | Feature Analysis                                                    |

|   |      | 6.3.4    | Prediction Analysis                                                 |

|   | 6.4  | Chapt    | er Summary                                                          |

| 7 | Faul | t Site F | Pruning for Practical Reliability Analysis of GPGPU Applications101 |

|   | 7.1  | Relate   | ed Work                                                             |

|   | 7.2  | Backg    | round and Methodology                                               |

|   |      | 7.2.1    | Baseline Fault Injection Methodology                                |

|   |      | 7.2.2    | Baseline Fault Model                                                |

|   |      | 7.2.3    | Statistical Considerations                                          |

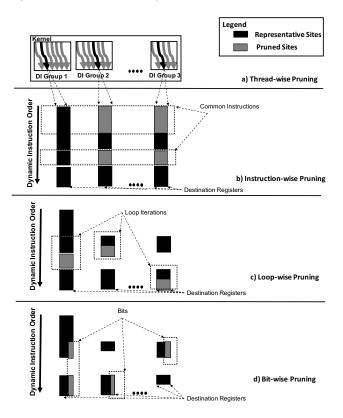

|   | 7.3  | Progre   | essive Fault Site Pruning                                           |

|   |      | 7.3.1    | Overview                                                            |

|   |      | 7.3.2    | Thread-Wise Pruning                                                 |

|   |      |          | 7.3.2.1 CTA-wise Pruning                                            |

|   |      |          | 7.3.2.2 Thread-wise Pruning                                         |

|   |      | 7.3.3    | Instruction-Wise Pruning                                            |

|   |      | 7.3.4    | Loop-Wise Pruning                                                   |

|   |      | 7.3.5    | Bit-Wise Pruning                                                    |

|   | 7.4  | Evalua   | ation                                                               |

|   | 7.5  | Multi-   | Bit Fault Injection                                                 |

|   |      | 7.5.1    | Assumptions                                                         |

|   |      | 7.5.2    | Extending Pruning to Multi-bit Fault Injection                      |

|   |      |          | 7.5.2.1 Extending to double-bit fault injection 132                 |

|   |      |          | 7.5.2.2 Extending to multi-bit fault injection                      |

|   |      | 7.5.3    | Evaluation                                                          |

|   |      |          | 7.5.3.1 Comparison of accuracy                                      |

|   |      |          | 7.5.3.2   | Impact of multi-bit faults                         |

|---|------|----------|-----------|----------------------------------------------------|

|   | 7.6  | Chapt    | er Summ   | ary                                                |

| 8 | АН   | ierarchi | cal Appro | each to Enabling Low-Overhead Reliable GPU Comput- |

|   | ing  |          |           | 139                                                |

|   | 8.1  | Relate   | ed Work   |                                                    |

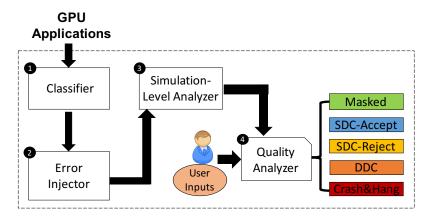

|   | 8.2  | Evalua   | ation Met | chodology                                          |

|   |      | 8.2.1    | Benchm    | arks and Evaluation Metrics                        |

|   |      | 8.2.2    | Evaluati  | ion Framework                                      |

|   | 8.3  | A Hier   | rarchical | Approach to Thread Classification                  |

|   |      | 8.3.1    | Multi-le  | vel Classification and Thread Selection            |

|   |      |          | 8.3.1.1   | CTA-level classification                           |

|   |      |          | 8.3.1.2   | Warp-level classification                          |

|   |      |          | 8.3.1.3   | Classification result and thread selection 153     |

|   | 8.4  | Hierar   | chical Ap | proach to Error Resilience Characterization 156    |

|   |      | 8.4.1    | Applicat  | tion Kernel Level Characteristics                  |

|   |      |          | 8.4.1.1   | Scope of accuracy-aware resilience                 |

|   |      |          | 8.4.1.2   | Sensitivity to input size                          |

|   |      | 8.4.2    | CTA Le    | vel Characteristics                                |

|   |      | 8.4.3    | Warp L    | evel Characteristics                               |

|   |      | 8.4.4    | Statistic | eal Validation                                     |

|   | 8.5  | Use C    | ase: Redu | ucing Protection Overhead                          |

|   | 8.6  | Chapt    | er Summ   | ary                                                |

| 9 | Futi | ure Wor  | k         | 168                                                |

|   | 9.1  | Fault 1  | Injection | for Multiple Inputs                                |

|   | 9.2  | Low-C    | verhead   | Reliable GPU Computing                             |

|   |      | 9.2.1    | Thread-   | to-CTA Remapping                                   |

| 9.2.2 | Resilience-Aware Scheduling |  |  |  |  |  |  |  |  |  | 171 |

|-------|-----------------------------|--|--|--|--|--|--|--|--|--|-----|

|       |                             |  |  |  |  |  |  |  |  |  |     |

#### ACKNOWLEDGMENTS

I would like to thank everyone who has helped with this thesis, especially:

My advisor, Professor Evgenia Smirni, who encourages me all the time, continuously teaches me new knowledge, and brings lots of chances to me to grow up in the research world. Without her patient guidance and persistent help, this thesis would not be possible.

My committee members, Professor Adwait Jog, Professor Xu Liu, Professor Bin Ren, and Professor Karthik Pattabiraman for their great support and insightful feedback and comments.

My intern mentors, Dr. Devesh Tiwari in Northeastern University, Dr. Mehran Kafai and Dr. Kave Eshghi in Hewlett Packard Enterprise, and Dr. Jianwu Xu and Dr. Hui Zhang in NEC Labs America. Without their guidance and help, I would not go through so many interesting and exciting projects.

All the faculty and staff at the Computer Science Department of the College of William and Mary. Special thanks to Vanessa Godwin, Jacqulyn Johnson, and Dale Hayes for their considerate and efficient assistance.

Ji Xue, Lishan Yang, Jacob Alter and many other dear friends for their support and help.

Finally, and foremost, I would like to give special thanks to my husband, Zhuo, for his understanding and encouragement, and my parents for their support throughout this research endeavor.

| I would like to dedicate this dissertation to my family, who provided endless support and love throughout my time at William and Mary. |  |

|----------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                        |  |

|                                                                                                                                        |  |

|                                                                                                                                        |  |

|                                                                                                                                        |  |

|                                                                                                                                        |  |

## LIST OF TABLES

| 2.1 | Comparison: 5 World's Most Powerful Supercomputers [15]                  | 10 |

|-----|--------------------------------------------------------------------------|----|

| 2.2 | Comparison: Titan vs. Blue Joule [15].                                   | 11 |

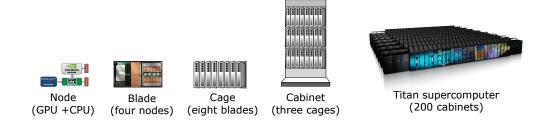

| 3.1 | Specifications and Features of the Titan Supercomputer [17]              | 22 |

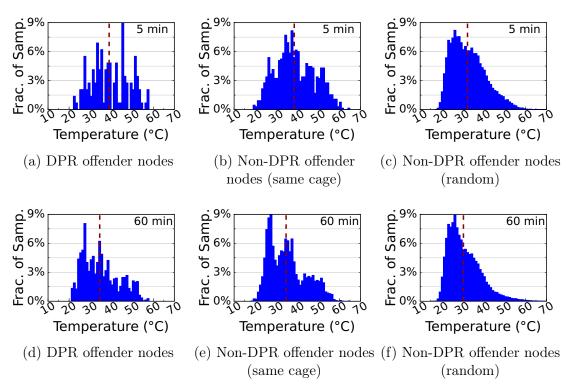

| 3.2 | Statistics for Temperature (°C) (DPR) $\dots \dots \dots \dots \dots$    | 41 |

| 3.3 | Statistics for Temperature (°C) (DBE)                                    | 45 |

| 4.1 | Temperature mean retention time for cabinets in different tempera-       |    |

|     | ture zones for GPU and CPU                                               | 52 |

| 4.2 | Statistics of temperature and power on Non-SBE offenders                 | 60 |

| 5.1 | Precision and recall for three neural networks                           | 75 |

| 5.2 | SBE Occurrence Prediction: Oracle vs. PRACTISE                           | 79 |

| 6.1 | Precision and recall for basic schemes                                   | 89 |

| 6.2 | F1 score for SBE occurrence prediction                                   | 93 |

| 6.3 | Mean training time for various models                                    | 94 |

| 6.4 | Effect from temporal and spatial aspects of temperature and power        |    |

|     | features                                                                 | 96 |

| 6.5 | SBE occurrence prediction for "short-running" and "long-running" ap-     |    |

|     | plications                                                               | 99 |

| 6.6 | Percentage of correctly classified SBE-affected application runs in four |    |

|     | severity levels.                                                         | 99 |

|     |                                                                          |    |

| 7.1 | Various metrics (including the total number of possible fault sites)       |

|-----|----------------------------------------------------------------------------|

|     | related to considered GPGPU application kernels                            |

| 7.2 | Fault sites and other statistics for GEMM                                  |

| 7.3 | CTA and threads groups for 2DCONV                                          |

| 7.4 | CTA and threads groups for HotSpot                                         |

| 7.5 | Effect of instruction-wise pruning for two threads                         |

| 7.6 | Summary of instruction-wise pruning for selected kernels. Other ker-       |

|     | nels do not exhibit instruction commonality                                |

| 7.7 | Statistics related to loops                                                |

| 8.1 | List of Applications with Evaluation Metrics and Thresholds 146            |

| 8.2 | The Impact of Different Inputs on CTA Group Popularity for HotSpot         |

|     | and RAY. Notation: GRP-S/M/L=the percentage of CTAs                        |

|     | in that group with Small/Medium/Large input, R=regular,                    |

|     | IR=irregular                                                               |

| 8.3 | CTA-level and Warp-level Classification for Benchmark Kernels. No-         |

|     | tation: $\%R\text{-}Grp.=\%$ regular groups over all groups, $\#$ $DI$     |

|     | $\mathit{Grp.}{=}\#$ of groups classified by dynamic instruction counts,   |

|     | # $\textit{ErrDist Grp.} = \#$ of groups refined by fault distribution 155 |

| 8.4 | Resilience Coverage vs. Overhead Reduction                                 |

## LIST OF FIGURES

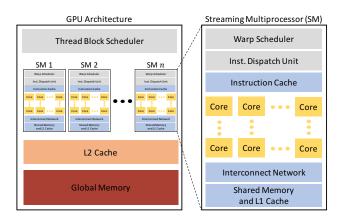

| 2.1 | A representative CUDA-based GPU architecture                          | 12 |

|-----|-----------------------------------------------------------------------|----|

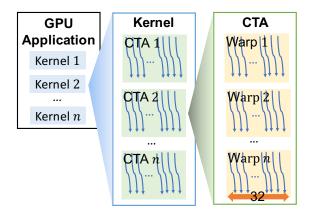

| 2.2 | A simplified overview of GPGPU application hierarchy                  | 13 |

| 3.1 | Overview of the Titan supercomputer's physical organization           | 22 |

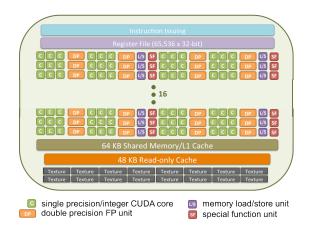

| 3.2 | Architecture of NVIDA K20X GPU deployed on the Titan supercom-        |    |

|     | puter [9]                                                             | 23 |

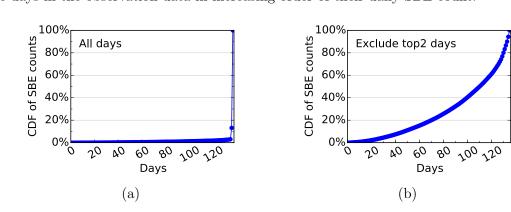

| 3.3 | Cumulative single bit error (SBE) count distribution over days (a),   |    |

|     | and cumulative SBE count distribution over days excluding top 2       |    |

|     | days (b)                                                              | 26 |

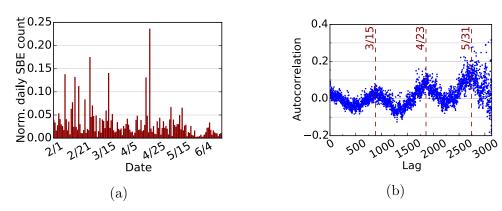

| 3.4 | Daily SBE count across time excluding the top two days (a), and       |    |

|     | autocorrelation function of the SBE interarrival times (b)            | 27 |

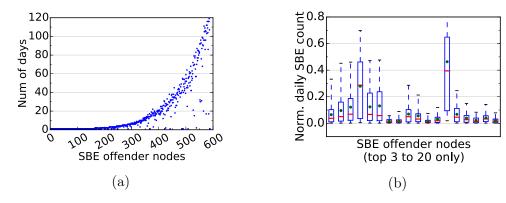

| 3.5 | Number of SBE-affected days for all nodes (sorted in increasing order |    |

|     | of total SBE count) (a), and normalized variation in the daily SBE    |    |

|     | count distribution for the top twenty SBE offender nodes excluding    |    |

|     | the top two nodes (red line in the middle represents median while     |    |

|     | green dot represents mean) (b)                                        | 29 |

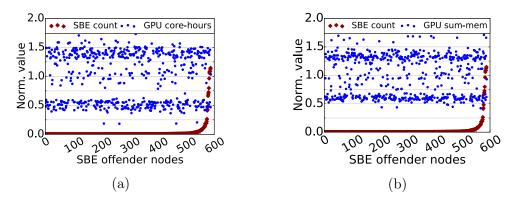

| 3.6 | GPU resource distribution for the SBE offender nodes (excluding top   |    |

|     | two SBE offenders): GPU core hours (a), and GPU memory utiliza-       |    |

|     | tion (b)                                                              | 30 |

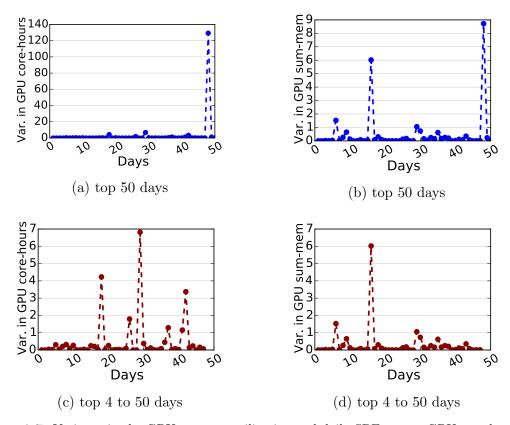

| 3.7  | Variance in the GPU resource utilization and daily SBE count: GPU     |    |

|------|-----------------------------------------------------------------------|----|

|      | core hours for top 50 days (a), for top 50 days excluding the top 3   |    |

|      | days (b), GPU memory utilization for top 50 days (c), and for top     |    |

|      | 50 days excluding the top 3 days (d). Days are sorted in increasing   |    |

|      | order of SBE count                                                    | 31 |

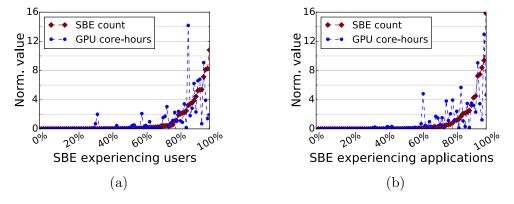

| 3.8  | GPU core-hours for users (a), and applications (b) experiencing SBEs. | 32 |

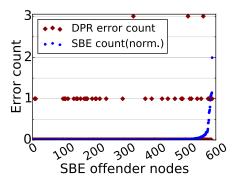

| 3.9  | DPR errors for SBE offender cards (excluding top two SBE offenders    |    |

|      | which had no DPRs)                                                    | 34 |

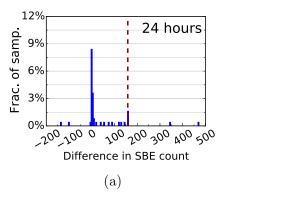

| 3.10 | Histograms of difference in SBE count for a 24-hour windows after     |    |

|      | and before the DPR occurrence for DPR offender nodes (a), and non-    |    |

|      | DPR offender nodes (b). Dotted vertical lines represent the average   |    |

|      | difference in SBE count                                               | 35 |

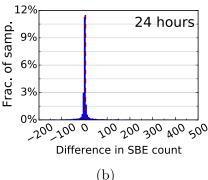

| 3.11 | Cumulative distributions of difference in SBE count for a 24-hour     |    |

|      | window (a) and a 72-hour window (b) for DPR offender nodes and        |    |

|      | non-DPR offender nodes. Some outliers are omitted for clarity. Omis-  |    |

|      | sion of outliers causes the DPR-curve not to approach 1               | 36 |

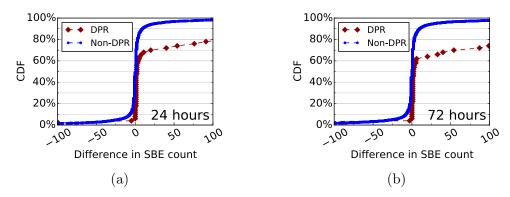

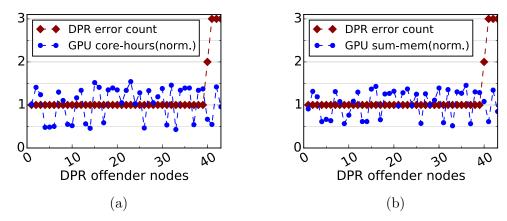

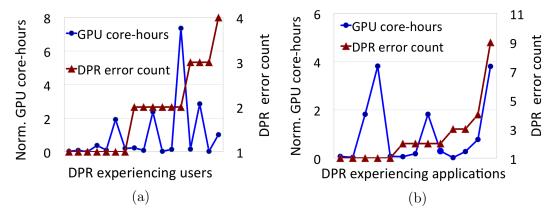

| 3.12 | DPR affected GPU nodes with increasing error counts and normalized    |    |

|      | GPU core-hours (a), and normalized GPU memory utilization (b)         | 37 |

| 3.13 | DPR errors and GPU core-hours for DPR affected users (a), and DPR     |    |

|      | affected applications (b)                                             | 38 |

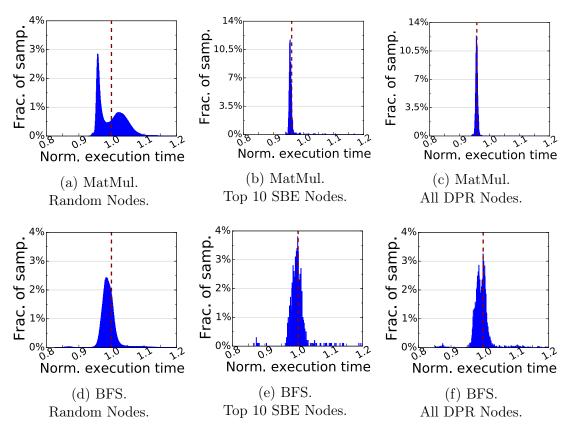

| 3.14 | Distribution of execution time on random nodes, top 10 SBE nodes,     |    |

|      | and DPR offending nodes                                               | 39 |

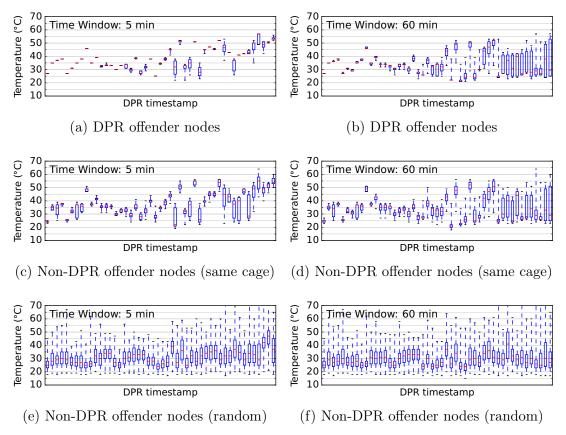

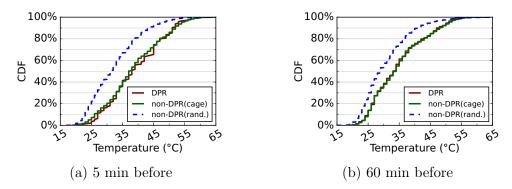

| 3.15 | Temperature variation before each DPR occurrence                      | 43 |

| 3.16 | Temperature variation before each DPR error                           | 44 |

| 3 17 | CDF of temperature variation before DPR errors                        | 44 |

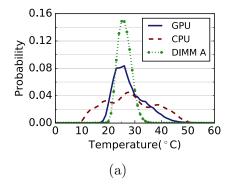

| 4.1  | (a) Histogram of temperature for GPUs, CPUs, and DIMMs. The                    |    |

|------|--------------------------------------------------------------------------------|----|

|      | average temperature of GPU, CPU and DIMM are $28.1^{\circ}C$ , $28.3^{\circ}C$ |    |

|      | and 26.1° $C$ , respectively. The standard deviation of GPU, CPU and           |    |

|      | DIMM are 6.1, 9.4 and 2.6, respectively. (b) Monthly Histogram of              |    |

|      | GPU temperature                                                                | 50 |

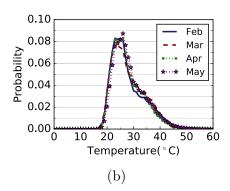

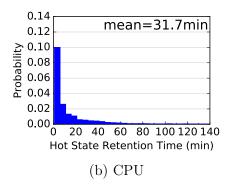

| 4.2  | hot state: retention time histogram for (a) GPU and (b) CPU. (Note             |    |

|      | that the long tail is truncated at 140min in both figures.)                    | 51 |

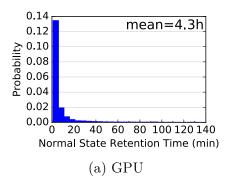

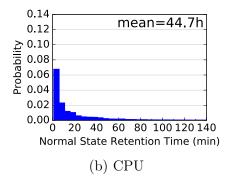

| 4.3  | normal state: retention time histogram for (a) GPU and (b) CPU.                |    |

|      | (Note that the long tail is truncated at 140min in both figures.) $$           | 51 |

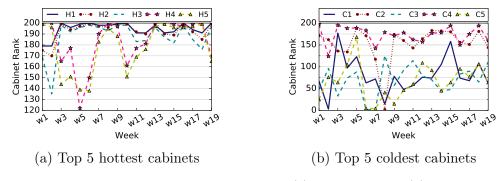

| 4.4  | Weekly ranking for five hottest (a) and five coldest (b) cabinets              | 53 |

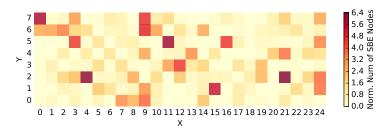

| 4.5  | Non-uniform distribution of GPU error offender nodes at the cabinet            |    |

|      | level                                                                          | 54 |

| 4.6  | Non-uniform distribution of SBE-affected application runs at the cab-          |    |

|      | inet level                                                                     | 54 |

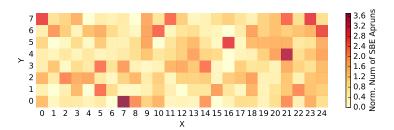

| 4.7  | Workload and GPU error distribution: a small set of workloads expe-            |    |

|      | rience most of the soft errors (a), and fraction of executions affected        |    |

|      | by SBEs for SBE-affected application runs (b)                                  | 55 |

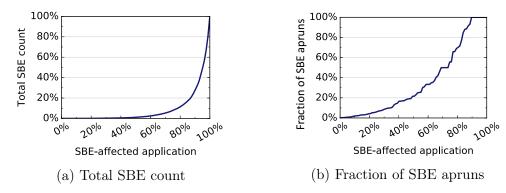

| 4.8  | Scatter plot of SBE count of SBE-affected application runs and their           |    |

|      | GPU utilization: core-hours (a) and memory (b)                                 | 56 |

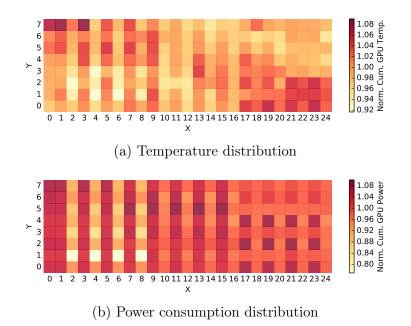

| 4.9  | Distribution of temperature (a) and power consumption (b) accumu-              |    |

|      | lative over the whole period at the cabinet level                              | 56 |

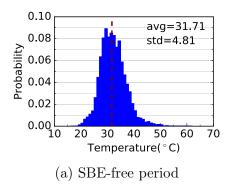

| 4.10 | Temperature distribution of SBE offender nodes during SBE-free pe-             |    |

|      | riods (a) and SBE-affected periods (b). Vertical lines represent mean          |    |

|      | values                                                                         | 57 |

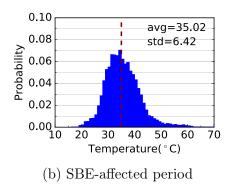

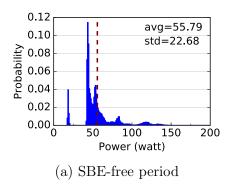

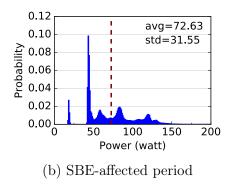

| 4.11 | Power consumption distribution of SBE offender nodes during SBE-               |    |

|      | free periods (a) and SBE-affected periods (b). Vertical lines represent        |    |

|      | mean values                                                                    | 58 |

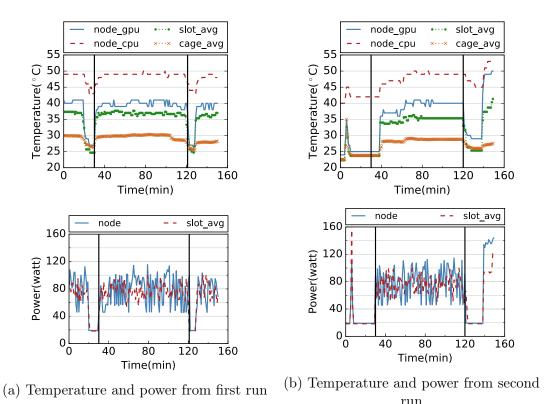

| 4.12 | Effect of neighboring components on temperature/power of an appli-                       |     |

|------|------------------------------------------------------------------------------------------|-----|

|      | cation over two runs on the same node overtime. Vertical solid lines                     |     |

|      | represent the start and end of the aprun execution                                       | 61  |

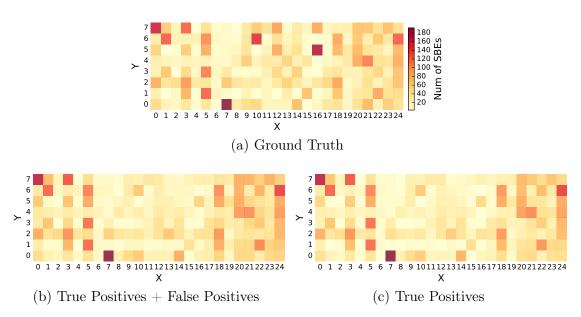

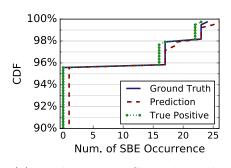

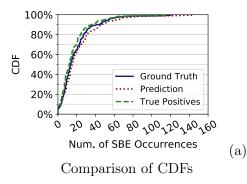

| 5.1  | SBE occurrence prediction at the cabinet level                                           | 76  |

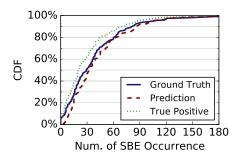

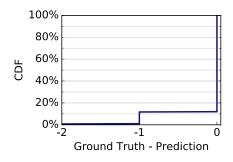

| 5.2  | Comparison between CDFs of ground truth, all prediction, and true                        |     |

|      | positives for SBE occurrences at the cabinet level                                       | 76  |

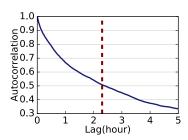

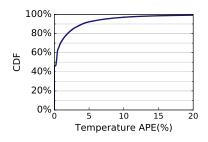

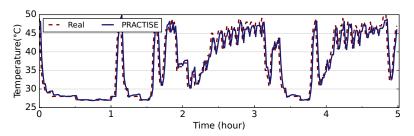

| 5.3  | Autocorrelation and PRACTISE prediction for temperature                                  | 78  |

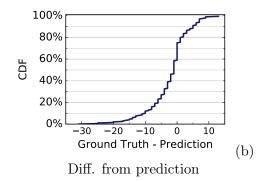

| 5.4  | Prediction for SBE occurrence at node level with PRACTISE                                | 79  |

| 6.1  | TwoStage method: prediction flow                                                         | 89  |

| 6.2  | Comparison of SBE occurrence prediction across different models for                      |     |

|      | DS1                                                                                      | 92  |

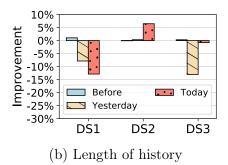

| 6.3  | Effect of different feature groups on F1 score, in terms of the im-                      |     |

|      | provement over Basic A. All means using all features discussed in                        |     |

|      | Section 6.1. <b>Hist</b> , <b>TP</b> , and <b>App</b> correspond to SBE history, temper- |     |

|      | ature/power consumption, and application-related features, respec-                       |     |

|      | tively                                                                                   | 95  |

| 6.4  | Decrement on F1 score if removing a certain feature set from the                         |     |

|      | original feature combination: global vs local (a), and different length                  |     |

|      | of SBE history (b).                                                                      | 97  |

| 6.5  | Comparison between SBE occurrence prediction and ground truth at                         |     |

|      | the cabinet level                                                                        | 98  |

| 7.1  | Overview of the 4-stage Fault Site Pruning Mechanism                                     | 111 |

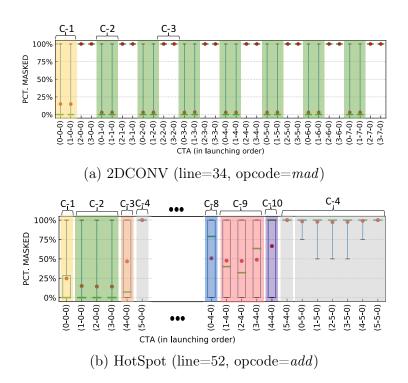

| 7.2 | CTA grouping after $60K$ fault injection runs of one target instruction  |

|-----|--------------------------------------------------------------------------|

|     | for (a) 2DCONV and (b) HotSpot. CTAs with the same color are             |

|     | classified into the same group. In the box plot, the horizontal green    |

|     | lines represent the median and red dots represent the mean 114           |

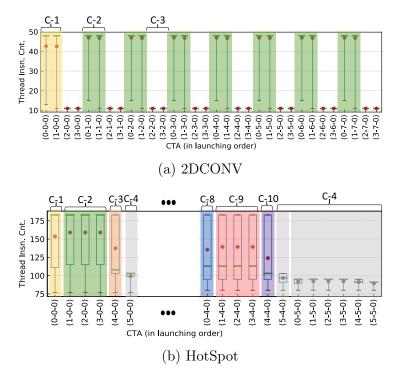

| 7.3 | CTA grouping given by average dynamic thread instruction count           |

|     | (iCnt) per CTA for (a) 2DCONV and (b) HotSpot. CTAs with the             |

|     | same color are classified into the same group. A significant similarity  |

|     | is is observed with Figure 7.2                                           |

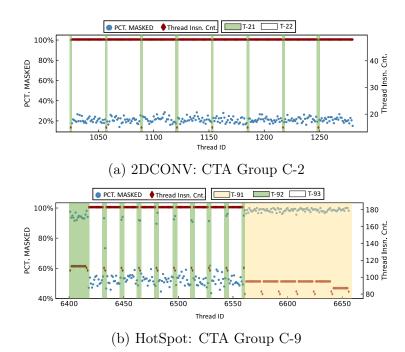

| 7.4 | Thread Grouping inside one CTA                                           |

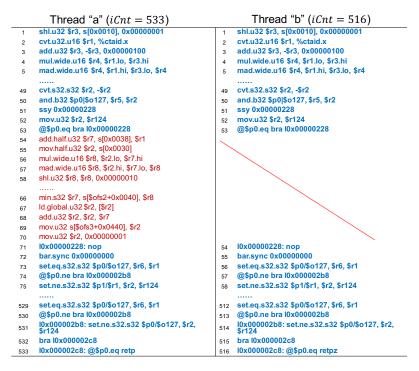

| 7.5 | PTXplus code comparison of two representative threads for                |

|     | PathFinder. Blue bold lines indicate common instructions 120             |

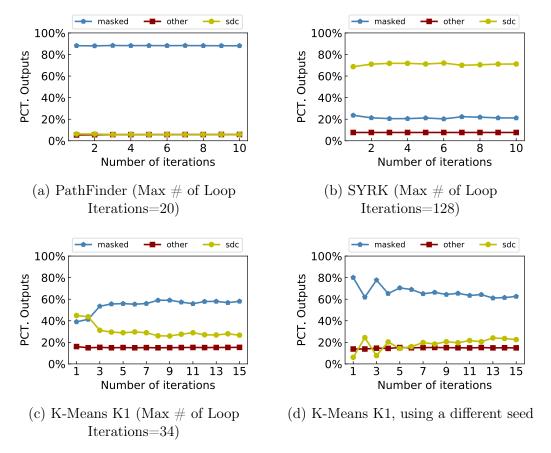

| 7.6 | Impact of loop-wise pruning on distribution of fault injection out-      |

|     | comes for (a) PathFinder, (b) SYRK, and (c)-(d) for K-Means K1           |

|     | with different random seeds                                              |

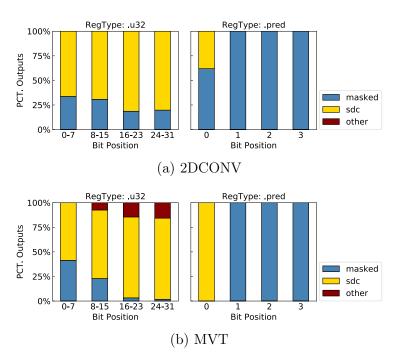

| 7.7 | Distribution of fault injection outcomes of different bit position sec-  |

|     | tions of two major register types (. $u32$ and . $pred$ ) for (a) 2DCONV |

|     | and (b) MVT                                                              |

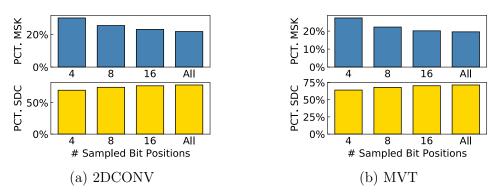

| 7.8 | Impact of bit-wise pruning on distribution of fault injection outcomes   |

|     | for (a) 2DCONV and (b) MVT (all registers). Percentage of outputs        |

|     | stabilizes at 16 bits                                                    |

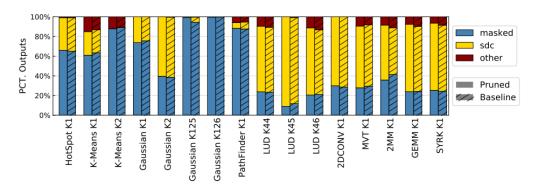

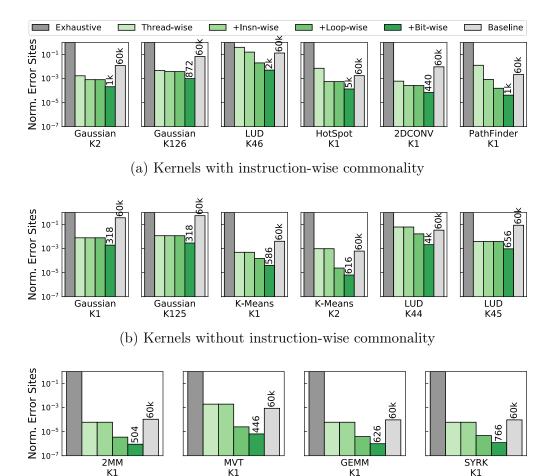

| 7.9 | Error resilience comparison of progressive fault site pruning tech-      |

|     | niques against the ground truth (baseline)                               |

| 7.10 | Fault site reduction comparison based on various feature-based prun-                                     |     |

|------|----------------------------------------------------------------------------------------------------------|-----|

|      | ing techniques. "+" indicates that each pruning stage is progressively                                   |     |

|      | built upon the pruned sites resulted from the previous stage. The                                        |     |

|      | height of the pruned fault sites bar is normalized by the original                                       |     |

|      | exhaustive fault sites for each application kernel, see last column of                                   |     |

|      | Table I. The effectiveness of progressive fault site pruning is compared                                 |     |

|      | against comprehensive baseline injection ( $60K$ random experiments).                                    |     |

|      | The exact numbers are shown on the top of the last two columns for                                       |     |

|      | the proposed method and the baseline case, respectively                                                  | 128 |

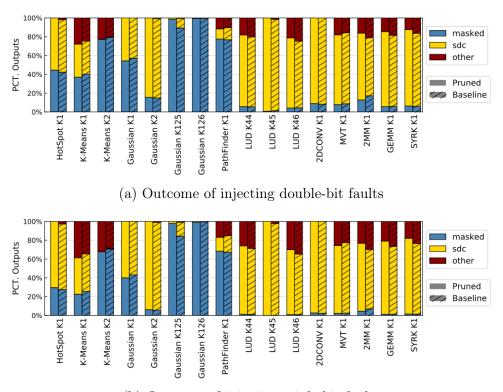

| 7.11 | Error resilience comparison of progressive fault site pruning tech-                                      |     |

|      | niques against the ground truth (baseline) for (a) injecting double-bit                                  |     |

|      | faults and (b) injecting triple-bit faults                                                               | 134 |

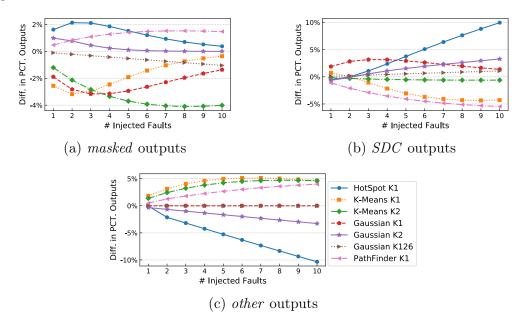

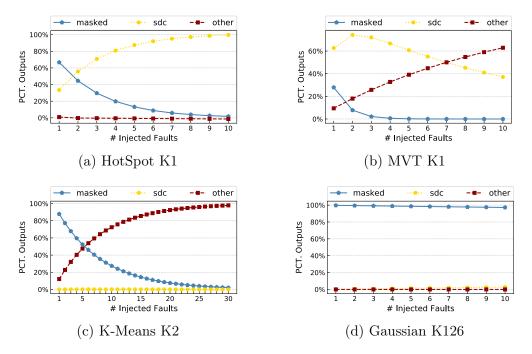

| 7.12 | Impact of increasing number of injected faults on the difference in                                      |     |

|      | terms of the percentage of (a) $\mathit{masked}$ , (b) $\mathit{SDC}$ , and (c) $\mathit{other}$ outputs |     |

|      | given by the proposed pruning technique and baseline for selected                                        |     |

|      | benchmark kernels                                                                                        | 135 |

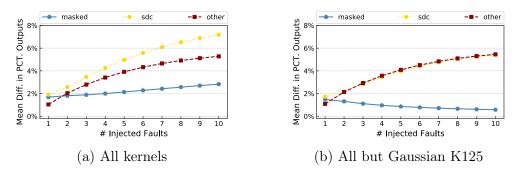

| 7.13 | Mean values of differences in terms of percentage numbers of differ-                                     |     |

|      | ent fault injection outcomes calculated (a) across all kernels and (b)                                   |     |

|      | across all kernels but excluding Gaussian K125                                                           | 136 |

| 7.14 | Error resilience changes over increasing number of injected faults for                                   |     |

|      | representative benchmark kernels                                                                         | 137 |

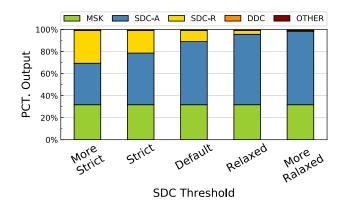

| 8.1  | Effect of a single bit fault on the BlackScholes application output                                      |     |

|      | shows that a significant percentage of the fault injection runs lead                                     |     |

|      | to silent data corruption (SDC), which can be acceptable to a user                                       |     |

|      | (SDC-Accept). The percentage of SDC-Accept increases as the user-                                        |     |

|      | defined acceptability threshold becomes less conservative                                                | 141 |

| 8.2  | A high-level view of fault injection and evaluation framework. $\ \ . \ \ . \ \ .$ | 147 |

|------|------------------------------------------------------------------------------------|-----|

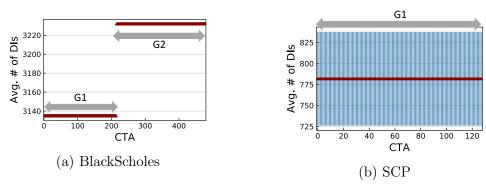

| 8.3  | Distribution of thread dynamic instruction (DI) counts at the CTA                  |     |

|      | level for regular benchmarks (a) BlackScholes and (b) SCP. The red                 |     |

|      | triangle indicates the average and the blue error bar indi-                        |     |

|      | cates one std                                                                      | 151 |

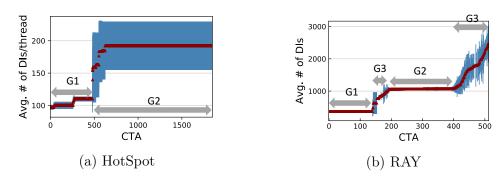

| 8.4  | Distribution of thread dynamic instruction (DI) counts at the CTA                  |     |

|      | level for irregular benchmarks (a) HotSpot and (b) RAY. The red                    |     |

|      | triangle indicates the average and the blue error bar indi-                        |     |

|      | cates one std                                                                      | 151 |

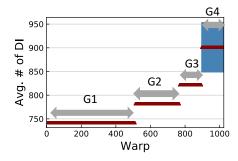

| 8.5  | Distribution of thread dynamic instruction counts at the warp level                |     |

|      | for SCP. The red triangle indicates the average and the blue                       |     |

|      | error bar indicates one std.                                                       | 153 |

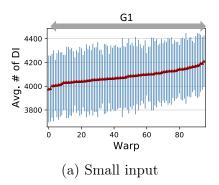

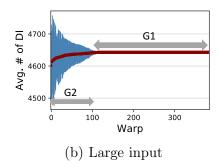

| 8.6  | Distribution of thread dynamic instruction counts at the warp level                |     |

|      | for MD k1, using two inputs: (a) Small and (b) Large. The red tri-                 |     |

|      | angle indicates the average and the blue error bar indicates                       |     |

|      | one std                                                                            | 154 |

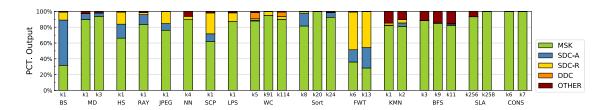

| 8.7  | Distribution of fault injection outcomes at benchmark kernel level.                |     |

|      | (SDC faults are evaluated with the default threshold values.)                      | 157 |

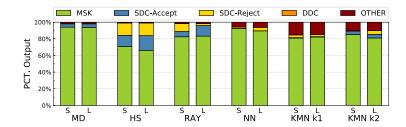

| 8.8  | Impact of Small and Large inputs on fault distribution                             | 158 |

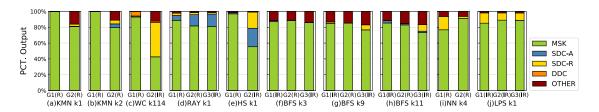

| 8.9  | Error resilience characteristics at CTA level. Each bar is distin-                 |     |

|      | guished by its group name and whether it is regular (R) or                         |     |

|      | irregular (IR)                                                                     | 160 |

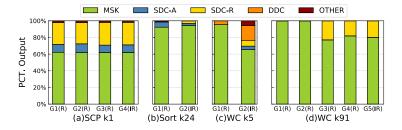

| 8.10 | Error resilience characteristics at warp level. Each bar is distin-                |     |

|      | guished by its group name and whether it is regular(R) or                          |     |

|      | irregular(IR).                                                                     | 161 |

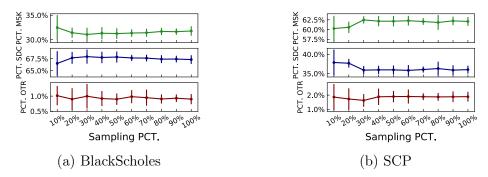

| 8.11 | Changes in the percentage of faults with increasing sample size for        |     |

|------|----------------------------------------------------------------------------|-----|

|      | (a) BlackScholes and (b) SCP. $PCT.MSK, PCT.SDC, $ and $PCT. OTR$          |     |

|      | indicate the percentage of masked, SDC, and other (including DDC,          |     |

|      | crashed, and hangs) faults, respectively. Error bars give the $95\%$       |     |

|      | confidence intervals.                                                      | 162 |

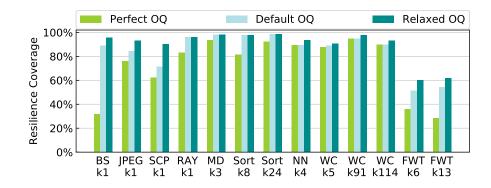

| 8.12 | Resilience coverage (% of $Masked + SDC\text{-}accept$ outputs) as a func- |     |

|      | tion of different output quality. Output quality changes with different    |     |

|      | SDC acceptability thresholds                                               | 166 |

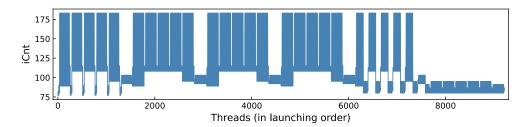

| 9.1  | The dynamic instruction count of threads in their launching order for      |     |

|      | HotSpot                                                                    | 170 |

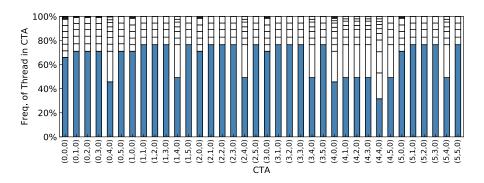

| 9.2  | The composition of threads with different dynamic instruction count        |     |

|      | inside each CTA for HotSpot. Each CTA contains 256 threads. None           |     |

|      | of the CTAs contains only one thread type while the colored part           |     |

|      | represents the dominant thread type.                                       | 170 |

## Chapter 1

# Introduction

Over the past decade, GPUs have become an integral part of mainstream high performance computing facilities. Parallelism provided by the GPU architecture has enabled domain scientists to simulate physical phenomena more quickly and accurately (i.e., at a finer granularity) [146, 79, 93] than what was previously possible by CPU-based large-scale clusters. Scientists are already benefiting from GPU deployment in large-scale computing systems such as the Titan supercomputer, the Blue Waters supercomputer, and the Keeneland cluster [146, 79, 69, 93]. Recognizing the performance and energy-efficiency benefits of GPUs, next generation pre-exascale supercomputers are also expected to continue taking advantage of parallelism provided by GPUs [13, 12]. Given the challenges of power provisioning for exascale systems, GPUs will continue to be an attractive choice due to their performance-per-watt characteristics that are better compared to their CPU counterparts [90].

Given the technology-trends and wide-spread adoption of GPUs, many researchers have studied the performance and energy-efficiency aspects of GPU-based applications in detail. In the meantime, the reliability of GPUs cannot be overlooked because most scientific applications are long-running, taking several hours or even days to complete. If software or hardware errors occur during application execution, they can not only lead to lower scientific productivity and operational efficiency of large-scale systems but can also

cause significant monetary loss [133]. Therefore, in addition to the principle of striving to achieve exascale performance at a stringent power budget, it is equal imperative to strive for more reliable GPU computing.

An initial step of any reliability study is to develop a deep understanding of GPU errors in the field. Computer architects have been investigating reliability characteristics of GPUs and ways to increase their reliability. Such efforts are often guided by technology projections and simplistic scientific kernels, and are performed using architectural simulators and modeling tools. Lack of large-scale field data impedes the effectiveness of such efforts. Only recently, researchers have started to investigate the reliability characteristics of GPUs using large-scale field data [140, 139, 92]. These recent studies have quantified the hardware and manufacturing-related failures of GPUs, firmware/application-related GPU errors, and how error resilience improves over generations of upgrades in GPU architecture. Still, as one of the most commonly observed errors, GPU soft errors (e.g., single-bit errors, double-bit errors, and dynamic page retirement errors), have not yet been studied well. There are many interesting aspects regarding GPU soft errors that are imperative to be explored, such as 1) the relationship between different types of GPU soft-errors, 2) the impact of soft-errors on application performance, and 3) the relationship between GPU soft-errors and user jobs, GPU resource utilization, temperature, and power consumption. Developing a better understanding on these aspects is the first focus of this dissertation.

Traditionally, the reliability of applications running on general-purpose GPUs is ensured with frequent check-pointing of application states [78] and error correction and detection codes for major GPU storage components (i.e., register files, shared memory, caches, and main memory). However, these protection mechanisms often come at high performance, power, and area costs [74, 155, 156, 75, 76]. For example, the impact of error-correcting code (ECC) overhead on real-world computational science applications can be as high as 10% on GPUs [26]. Nevertheless, the decreased memory bandwidth caused by ECC overhead can result in larger performance degradation than the decreased fraction of bandwidth itself due to queuing. Facing such expensive reliability overhead in

large-scale systems, computational scientists already naively turn off ECC for their application runs [53]. Still, completely turning off error protection can be too risky. In such cases, a prediction model that can accurately forecast the occurrences of GPU soft-errors would be useful in guiding flexible error protection mechanisms for GPU nodes, e.g., by dynamically turning on/off error protection based on prediction. Acknowledging the necessity of an error predictor, the second focus of this dissertation is to elaborate on the challenges, process, and solutions involved in building effective error prediction models. Specifically, we consider features that are related to the occurrences of GPU soft errors guided by our large-scale reliability analysis in the field. We observe that the relationship is rather complex and is non-trivial to be exploited by straight-forward statistical models. Therefore, we leverage machine learning models to capture such complicated interactions between system/application features and the prediction target (i.e., soft-error occurrences). Through our evaluation, the proposed models are able to accurately forecast the occurrences of soft errors on GPU nodes.

The aforementioned characterization and prediction efforts towards GPU soft errors are performed at the system level. Such coarse-grained reliability analysis is beneficial in terms of acquiring an overview on the GPU soft errors in the field and of developing system-level solutions to improve system reliability. Still, such analysis has its inherent drawbacks. First, large-scale system measurement data in the wild are post hoc and we have limited control over the data collection methodology, i.e., our analysis is subject to the data and information provided by Titan's system administrators. Second, we have no knowledge regarding the applications running on the system, except for their binary executable file names. Unfortunately, the lack of application-related information impedes us from any further exploration towards specific application types. To understand the effects of soft errors on specific applications, we do fine-grained reliability analysis on a wide set of popular GPGPU benchmarks to understand why applications react to GPU soft errors differently, that is we aim to explore the different error resilience characteristics of GPGPU applications. This is the third focus in this dissertation.

There is a rich body of prior work studying the error resilience characteristics of GPU applications [154, 85, 44, 59]. These works propose different kinds of fault-injection models to systematically inject faults to diverse locations (i.e., registers) in applications (commonly referred to as fault sites) and evaluate the tolerance of applications in the presence of GPU errors. One of the major challenges in building an effective fault-injection model is fault sites selection, i.e., injecting faults in all possible fault sites and explore their effect. Suppose we consider a single-bit flip model that injects one fault per application execution, which is the de-facto model used in studies in this area [154, 44, 59] and is shown to be effective and sufficient in capturing the error resilience characteristics of GPU applications [124], the total number of exhaustive fault injection sites for benchmarks in commonly used benchmark suites (i.e., CUDA [110], Rodinia [31], and Polybench [54]) can range from millions to even billions, such as  $3.44 \times 10^7$  for HotSpot [31] and  $6.23 \times 10^8$ for GEMM [54], and  $6.38 \times 10^9$  for BlackScholes [110]. The tremendous size of fault sites is due to the fact that each GPGPU application kernel can spawn hundreds to thousands of threads and each thread is assigned to a dedicated amount of on-chip resources (e.g., register files, ALUs, and shared memory). For the calculation of fault sites reported above, we only consider soft errors that occur in functional units (e.g., arithmetic logic unit and load-store unit), which are not protected in current commercial GPUs [4, 8, 10]. Yet, the number of fault sites is tremendous. Executing one experiment per fault site in such a vast space to collect application reliability metrics is clearly impossible and absolutely not practical.

Consequently, it is imperative to first resolve this challenge of how to systematically and efficiently reduce the number of fault sites required in a fault-injection campaign. Facing this challenge, prior works [85, 44, 59] mainly resort to statistical solutions, such as randomly selecting a number of fault sites based on the desired error margin and confidence interval [83]. Such statistical methods have two limitations. First, a large number of fault sites is required to deliver statistically significant results. For example, it is necessary to conduct 60K experiments to achieve a confidence interval of 99.8% and an error mar-

gin of 1.26% [83]. Second, this method gives no intuition about fault site selection from the architecture perspective, such as whether different GPGPU application resources react similarly or differently to faults. In this dissertation, we take an orthogonal approach, by pruning the large amount of fault sites via carefully considering the properties of GPGPU applications. By carefully selecting pruning mechanisms, we aim to reduce the total number of required fault sites while still maintain accuracy in capturing GPGPU application resilience characteristics. Naturally, this framework can serve as a tool to deepen the understanding on the error resilience characteristics of GPGPU applications.

Note that, this framework is build on the commonly used single-bit fault model [154, 44, 59], the next natural step is to extend it to multi-bit fault model, especially for GPGPU applications. Previous studies have looked into the impact of multi-bit faults for CPU applications [124]. However, GPGPU applications normally spawn many more threads than CPU applications, making it non-trivial to directly apply those techniques to GPGPU applications. Therefore, in this dissertation, we also investigate the impact of multi-bit faults on the outcomes of GPGPU applications by extending the proposed framework to the multi-bit fault model.

Lastly, inspired by the proposed framework, we devise a hierarchical approach to study the error resilience characteristics of GPGPU applications at three different levels, including kernel levels, CTA levels, and warps levels. We observe that CTAs (or warps) show different resilience features. In other words, some CTAs (or warps) are very error resilient while others are sensitive to soft errors. In addition, we notice that not all corrupted application outputs due to soft errors are unacceptable to the end users. If users are willing to sacrifice some output quality, there would be sufficient opportunities for providing low-overhead and reliable GPGPU error protection strategies.

#### 1.1 Contributions

The contributions of this dissertation are summarized as follows:

- System-level GPU reliability analysis [101, 102, 103]: We conduct a large-scale study on GPU soft-errors on a real-world in-production HPC system the Titan supercomputer, which is America's fastest supercomputer for open science [18]. We discover features with indicative capability of GPU errors and exploit them for error occurrence prediction.

- Application-level GPU reliability analysis [104, 100]: We investigate the effect of GPU errors on application execution by first proposing a systematic way of progressively pruning the fault site space for a doable and practical fault injection campaign.

#### 1.1.1 GPU Reliability Analysis at the System Level

- We perform a large-scale study on GPU soft-errors on the Titan supercomputer, including single-bit errors (SBEs), double-bit errors (DBEs), and dynamic page retirement errors (DPRs). We investigate their characteristics and relationship with GPU resource utilization, applications, users, and temperature, as well as the relationship between different types of errors [101].

- We conduct a deep exploration on the most commonly observed errors single-bit errors (SBEs) [102, 103]. We discover that workload characteristics, certain GPU cards, temperature and power consumption have complex interaction with GPU SBEs.

- We propose two effective machine-learning-based predictors that are able to accurately forecast the occurrences of GPU SBEs [102, 103]. More specifically,

- We show how to systematically select input features for prediction models by categorizing them into spatial and temporal dimensions [103].

- We acknowledge the presence of imbalanced dataset in the Titan traces and overcome this challenge with a customized similarity-reduction-based algorithm that is capable of under-sampling the majority class [102].

- We devise a neural-network-based prediction framework [102] to forecast GPU

SBE occurrences.

- We devise a two-stage prediction framework by taking advantage of the inherent dataset features and evaluate its effectiveness across several machine learning models [103].

#### 1.1.2 GPU Reliability Analysis at the Application Level

- We quantify the problem of high number of fault sites in the fault-injection campaign for GPGPU applications [104].

- We develop progressive pruning techniques by leveraging GPGPU-specific properties, such as similarity in terms of resilience characteristics in threads, commonality in common code blocks, presence of large portion of loop iterations, and relationship between resilience features and location of bits in the registers. With the proposed solution, we are able to reduce the fault space by up to seven orders of magnitude while maintaining accuracy that is close to the ground truth [104].

- We extend the proposed fault site pruning technique to multi-bit fault model and evaluate the accuracy via various GPGPU benchmarks.

- We come up with a hierarchical approach to study the error resilience characteristics

of GPGPU applications at various levels, including kernel level, CTA level, and warp

level. We observe that different CTAs (or warps) exhibit different error resilience

characteristics [100].

- Giving the fact that not all corrupted GPGPU application outputs are unacceptable to the user, we are able to strike the balance between reducing error protection overhead and preserving acceptable application output quality at the kernel, CTA, and warp levels [100].

### 1.2 Organization

This dissertation is organized as follows. In Chapter 2, we present the background and basic concepts that are used in this dissertation. In Chapter 3, we present a large-scale study of soft-errors on GPUs in the field [101]. In Chapter 4, we focus on the most commonly observed GPU soft-errors, that is single-bit errors (SBEs), and investigate their complex interaction with several related features [102, 103]. In Chapter 5 and 6, we introduce two machine-learning-based solutions to predict SBE occurrences [102, 103]. In addition to the study of GPU reliability at the system level, in Chapter 7 we turn to understand the resilience features of GPGPU applications, by starting with designing an effective fault injection framework with progressively pruned fault sites, for both single-bit and multi-bit fault models [104]. Then, in Chapter 8, we show a hierarchical approach to understanding error resilience characteristics of GPGPU applications at kernel, CTAs, and warps levels and illustrate opportunities of enabling low-overhead yet reliable GPGPU computing through a use case [100]. Finally, in Chapter 9, we describe future research directions.

## Chapter 2

# Background and Related Work

In this chapter, we introduce basic concepts and terminology that are used in the entire dissertation. First, we present the prevalent adoption and the benefits of accelerators, especially GPUS, on large-scale systems (see Section 2.1). Then, in Section 2.2, we explain the background knowledge related to GPUs. Lastly, we discuss related work on GPU reliability analysis in Section 2.3.

### 2.1 Benefits of Accelerators on Large-Scale Systems

Recently, supercomputers have been providing powerful computational capability for scientific applications from diverse domains, such as science, engineering, medicine, social media, gaming, and finance [41, 119, 136, 46, 125, 112, 106, 109]. For years, researchers keep pushing the envelop on the maximum and peak computational speed of supercomputers, reflecting as the constantly fluctuating ranks on the Top500 list [18]. On the other hand, supercomputers are normally costly. They require huge power for computation and on cooling. Consequently, power efficiency (i.e., performance-per-watt) is becoming important complement metric to compare supercomputers, yielding in another fierce competition in Green500 list [15].

Table 2.1 presents the 5 most powerful supercomputers in the world (as of November, 2017) [18, 15]. Surprisingly, we notice that Tianhe-2 (launched in 2013) and Titan

(launched in 2012) still provide superior computational capability that outperform a lot of newly-launched systems. From the table, we make several observations:

Table 2.1: Comparison: 5 World's Most Powerful Supercomputers [15].

| Top500/<br>Green500<br>Rank | Name                        | Country,<br>Year          | Total<br>Cores       | Rmax<br>[TFlop/s] | Rpeak<br>[TFlop/s]   | Power (kW)           | Power<br>Effeciency<br>[GFlops<br>/Watts] | Accelerator/<br>Co-Processor |

|-----------------------------|-----------------------------|---------------------------|----------------------|-------------------|----------------------|----------------------|-------------------------------------------|------------------------------|

| 1/20                        | Sunway Tai-<br>huLight [48] | China,<br>2016            | 1.1e+07              | 9.3e+04           | 1.3e+05              | 1.5e+04              | 6.05                                      | None                         |

| 2/137                       | Tianhe-2 [16]               | China,<br>2013            | 3.1e+06              | 3.4e+04           | $5.5\mathrm{e}{+04}$ | 1.8e + 04            | 1.90                                      | Intel Xeon<br>Phi 31S1P      |

| 3/10                        | Piz Daint [11]              | Switzer-<br>land,<br>2017 | 3.6e+05              | 2e+04             | $2.5\mathrm{e}{+04}$ | $2.3\mathrm{e}{+03}$ | 10.40                                     | NVIDIA<br>Tesla P100         |

| 4/5                         | Gyoukou [6]                 | Japan,<br>2017            | $2.0\mathrm{e}{+07}$ | 1.9e+04           | $2.8\mathrm{e}{+04}$ | $1.4e{+03}$          | 14.17                                     | PEZY-SC2<br>700Mhz           |

| 5/105                       | Titan [17]                  | USA,<br>2012              | $5.6\mathrm{e}{+05}$ | 1.8e+04           | 2.7e+04              | 8.2e+03              | 2.14                                      | NVIDIA<br>Tesla K20x         |

Rmax - Maximal LINPACK performance achieved; Rpeak - Theoretical peak performance. Rank is as in November, 2017.

First of all, except the top first supercomputer – Sunway TaihuLight, all others are assisted with accelerators or co-processors to boost achievable performance. Note that, the Top500 list is ranked by Rmax (i.e., maximal performance achieved). When looking at Ppeak (i.e., theocratical peak performance), Sunway TaihuLight is beaten by all the other four, including the two launched in 2012/2013. This indicates the powerful performance boosting ability provided by accelerators/co-processors.

Most importantly, if we focus on the power efficiency (i.e., performance per watt), we further acknowledge the importance of deploying accelerators/co-processors. Gyoukou and Piz Daint are very power-efficient by achieving a score over 14.17 GFlops/Watts and 10.40 GFlops/Watts, respectively. They mainly benefit from accelerators. Piz Daint is equipped with NVIDIA Tesla P100 [14], a powerful general-purpose GPU that is specially designed for compute-intensive and high-parallel applications. Gyoukou uses PEZY-SC2 [34], a very close cousins of GPU chips. Moreover, it is worth mentioning that Titan (with power efficiency of 2.14 GFlops/Watts) and Tianhe-2 (with power efficiency of 1.90 GFlops/Watts) surprisingly beat Sunway TaihuLight (with power efficiency of 6.05 GFlops/Watts). In

fact, if we look at supercomputers launched in 2012, Titan has the close-to-best power efficiency but superior computational capability, as compared with the most power-efficient supercomputer Blue Joule at that time (see Table 2.2). A noticeable difference between the two supercomputers is that Titan accelerates by GPUs while Blue Joule does not. These evidences show that accelerators/co-processors play an important role in building power-efficient supercomputers.

Table 2.2: Comparison: Titan vs. Blue Joule [15].

| Top500/<br>Green500<br>Rank | Name           | Country,<br>Year | Total<br>Cores | Rmax<br>[TFlop/s]    | $\begin{array}{c} {\rm Rpeak} \\ {\rm [TFlop/s]} \end{array}$ | Power (kW) | Power<br>Effeciency<br>[GFlops<br>/Watts] | Accelerator/<br>Co-Processor |

|-----------------------------|----------------|------------------|----------------|----------------------|---------------------------------------------------------------|------------|-------------------------------------------|------------------------------|

| 5/105                       | Titan [17]     | USA,<br>2012     | $5.6e{+05}$    | 1.8e+04              | 2.7e+04                                                       | 8.2e+03    | 2.14                                      | NVIDIA<br>Tesla K20x         |

| 88/92                       | Blue Joule [2] | UK,<br>2012      | 1.3e+05        | $1.4\mathrm{e}{+03}$ | 1.7e + 03                                                     | 6.6 e + 02 | 2.18                                      | None                         |

Rmax - Maximal LINPACK performance achieved; Rpeak - Theoretical peak performance. Rank is as in November, 2017.

Inspired by the success of deploying accelerator/co-processors on high-performance computing systems, two more powerful next-generation supercomputers are being deployed – Summit [13] on Oak Ridge National Lab and Sierra [12] on Lawrence Livermore National Lab, both are expected to in operation in 2018.

Acknowledging the necessity of accelerators/co-processors in achieving both powerful computational ability and power efficiency, we focus in this dissertation on the most commonly-used accelerators—general-purpose GPUs (or GPUs in short) [18, 15].

### 2.2 General-Purpose GPUs for Scientific Computing

In this section, we introduce the concepts and background knowledge for general-purpose GPUs (or GPUs for short). Throughout the dissertation, we use CUDA-based terminology (CUDA stands for Compute Unified Device Architecture [1]) created by NVIDIA as NVIDIA GPUs are widely-used in the field. In fact, among the supercomputers with

accelerators/co-processors in Top500 List, over 85% are boosted with NVIDIA Tesla GPUs [18].

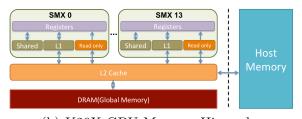

#### 2.2.1 Baseline GPU Architecture

Figure 2.1 shows a representative CUDA-based GPU architecture. A typical GPU consists of multiple simple cores, also called streaming-multiprocessors (SMs) in NVIDIA terminology [111]. Each core is associated with private L1 data, texture and constant caches, software-managed scratchpad memory, and register files. Cores are connected to memory channels (partitions) via an interconnection network. Each memory partition is associated with a shared L2 cache, and its associated memory requests are handled by a GDDR5 memory controller. Recent commercial GPUs, i.e., Fermi [8], Kepler [10] and Pascal [4], use unified single-error-correction double-error-detection (SEC-DED) error correction codes (ECCs) to protect register files, L1/L2 caches, shared memory and DRAM from soft errors, and use parity to protect the read-only data cache. Other structures like arithmetic logic units (ALUs), thread schedulers, instruction dispatch unit, and interconnect network are not protected.

Figure 2.1: A representative CUDA-based GPU architecture.

#### 2.2.2 GPGPU Applications and Execution Model

GPGPU applications rely on the single-instruction-multiple-thread (SIMT) philosophy and concurrently execute thousands of threads over large amounts of data to achieve high throughput. Figure 2.2 presents a simplified overview of thread hierarchy in GPGPU applications. A typical GPGPU application execution starts with the launch of kernels on the GPU. Each kernel is divided into groups of threads, called thread blocks, which are also known as Cooperative Thread Arrays (CTAs) in CUDA terminology. A CTA encapsulates all synchronization and barrier primitives among a group of threads [77, 67]. Having such an abstraction allows the underlying hardware to relax the execution order of the CTAs to maximize parallelism. The underlying architecture sub-divides each CTA into groups of 32 individual threads (called warps) that execute a single instruction on the functional units in lock step. This sub-division is an architectural abstraction and is transparent to the application programmer.

Figure 2.2: A simplified overview of GPGPU application hierarchy.

#### 2.2.3 GPU Errors in the Field

GPU errors can be classified into several categories. GPU hardware related errors, such as double bit errors, off-the-bus errors, and micro-controller halts cause the application to crash. Soft errors that can be corrected by the ECC mechanism do not result in execution

loss. Single bit errors are corrected by the SECDED ECC. Two single bit errors on the same page result in a dynamic page retirement (DPR) error [108]. This particular error is also reported when a double bit error happens and the page is retired in order to improve the longevity of the card.

There is a host of GPU related errors including errors that are caused by the application, driver issues, firmware bugs, or thermal issues. Note that NVIDIA documents a list of such XID errors and their possible causes [19]. GPU applications may also terminate with a non-zero exit code, indicating that the execution was not successful. Other than hardware-related and XID errors, several other reasons may be responsible for non-zero exit codes, e.g., programming errors and expiration of time-quota. Prior works [55, 139] study these XID errors and system-integration errors (e.g., Off the Bus).

#### 2.3 Reliability Analysis in the Field

In the Section 2.1, we give an overview of the performance/power efficiency benefits of deploying GPU accelerators in supercomputers. Reliability of such large-scale systems is equally worthy of research attention, especially since the scientific applications running on these systems are typically long-running [140, 139]. Any software or hardware error that occurs during application execution decreases the scientific productivity and operational efficiency and could result in significant monetary loss [133]. Therefore, it is important that applications are able to cope with different types of runtime failures and errors. As we progressing towards exascale, applications are going to face even more severe resilience challenges, due to the increasing number and decreasing size of the components required for exascale systems [90]. In this section, we discuss past work on reliability analysis from two perspectives: large-scale system level (see Section 2.3.1) and application level (see Section 2.3.2).

#### 2.3.1 System-Level Reliability Analysis

Quantifying and characterizing system failures is key to improving the reliability of any computing system. This is even more important for large-scale computing systems since the impact of system failures is large on these system and may lead to significant scientific productivity and monetary loss. Consequently, researchers have investigated failures on large-scale systems in detail [92, 42, 88, 89, 113, 117, 123, 128]. Several studies have exploited the insights from such efforts to predict failures and adapt fault-tolerance mechanisms to minimize the impact of system failures. Some of these studies propose to predict failure by identifying the correlation among failure events [49, 50, 51, 88]. Such proposals often rely on machine learning and other prediction techniques on the RAS logs and the system logs. This may result in high-overhead and low lead time for prediction, but nevertheless they demonstrate that failure prediction is possible and effective in certain cases.

Several studies have focused on studying the reliability aspect of large-scale computing systems. For example, Liang et al. investigated different component failures including network, disk, memory and CPU for the Blue Gene/L system, and proposed failure prediction models [88]. Oliner et al. investigated system failure logs for multiple HPC systems at the Los Alamos National Laboratory and the Sandia National Laboratory, including Red-Storm and Thunderbird system [113]. They studied both software and hardware errors and developed a methodology for applying filtering of failure logs. Schroeder et al. have studied the system failures and its impact on multiple HPC systems at LANL [128].

There have also been more failure studies for a given system component such as DRAM, disks, and SSDs. For example, DRAM-focused efforts have shown the effect of vendors on soft-errors [62, 129, 135]. These studies also show the pitfalls in studying the DRAM errors and its impact on the reliability assessment of the system. Disk-focused studies demonstrate that disk failures in the field can be significantly higher than what one would estimate from the vendor's sheet [126, 23]. Such studies also show that peripheral components fail

more often than one may expect in large scale storage systems. Recent studies [95] on SSD failure in the field provide insights about differences in the early detection life cycle between SSDs and Disks, lack of read disturbance error in the wild, and implication of these findings for future SSDs. However, large-scale GPU reliability characterization studies have been relatively limited [57, 92, 140], primarily because the GPU architecture is a relatively newer technology.

Recently, there have been efforts focusing on studying and improving GPU reliability at scale [25]. Several recent studies [92, 140, 139] present error characterization for the GPU-enabled Cray supercomputers such as the NCSA Blue Water and Titan supercomputer. They study the spatial and temporal characteristics of GPU errors, how these errors propagate spatially in a short time-window, frequency of GPU errors in different memory structures of a GPU, correlation between batch jobs and correctable GPU errors, etc. These efforts have primarily focused on understanding XID errors, manufacturing errors (e.g., Off the Bus error), and its effect on application-execution. These studies have also shown via neutron beam testing that more recent generation of GPUs are more error resilient than previous generation of GPU architecture. These studies have also focused on issues and challenges with current GPU error logging methods. Previous efforts by Haque et al. [57] have deployed a software-based GPU soft-error detector on Folding@home distributed platform for two different architectures, the G80 and GT200 architectures. They showed that newer generation of GPUs observed significantly lower soft error rate. Additionally, they found that the GPUs were sensitivity to memory faults in a pattern-dependent manner.

Limitations of prior work: None of the aforementioned studies present detailed analysis and characterization of soft-errors on GPUs at large-scale, especially the most commonly observed single-bit errors. It is important to understand the complex interplay between GPU errors and related factors (i.e., workloads, resource utilization, temperature, and power consumption). Such understanding helps strike a balance in reducing resilience overhead and preserving reliability, i.e., by building effective error prediction frameworks.

#### 2.3.2 Application-Level Reliability Analysis

Besides the preceding system-level reliability studies, researchers have also leveraged simulation-based analysis to detect critical hardware structures that are more vulnerable to soft errors. In particular, prior works [45, 64, 138] have conducted architectural vulnerability analysis (AVF), which tracks every bit in an architecture during the application run and calculates the likelihood of the bit that can affect the output. In addition, fault-injection models are also effective in understanding the impact of faults. Although there is a large body of prior work on fault injection models/frameworks [92, 42, 88, 89, 113, 117, 123, 128, 126, 23, 95, 49, 50, 51] in the context of CPUs, only a limited set of fault injector models have been proposed for GPUs. Yim et al. [154] built a source-to-source translator, SWIFI, to investigate error resilience in GPUs and demonstrate that the ratio of silent data corruption (SDC) in GPUs is much higher than that observed in CPUs. In order to capture the impact of faults at the architecture level, Fang et al. [44] developed GPU-Qin that leverages the GPU debugging tool cuda-gdb [3] to inject one fault into the destination operand or the address operand of arithmetic and memory instructions. However, since GPU-Qin uses cuda-qdb, it cannot inject faults into control flow instructions. Hari et al. [59] addressed this problem with a compiler-based fault injection framework, SASSIFI, which injected single bit errors into the destination operand of any kind of assembly instructions.

Limitations of prior work: Prior work mainly focuses on developing fault injection models using compiler-based or simulation-based tools. In terms of fault sites selection, these works mostly randomly sample a tiny subset of all potential fault injection locations in the application, whose size is often in the magnitude of millions to billions, to capture a view of the overall resilience characteristics for GPGPU applications [83]. For example, with 95% confidence interval and error margin of 6%, it is necessary to launch around 1000 fault injection runs. The number increases to 60K when seeking a more strict requirement, i.e., 99.8% confidence interval and error margin of only 1.26% [83]. However, such fault

site selection methodology impedes any deeper resilience analysis at the kernel, CTA, and warp levels. In addition, it would be also interesting to see if we can deliver the same resilience characteristics with fault sites with less than 60K or even less than 1K samples, which is the focus of this dissertation.

#### 2.4 Chapter Summary

In this chapter, we first show the benefits given by the prevalent adoption of GPUs in large-scale systems. Then, we discuss prior efforts in understanding the reliability of GPUs that motivate and guide the research presented in this dissertation. Finally, we explain useful GPU-related knowledge.

## Chapter 3

## A Large-Scale Study of Soft-Errors on GPUs in the Field

In this chapter, we describe a large-scale investigation on GPU soft-errors in the filed by analyzing large amount of measured system related data on the Titan supercomputer, which is America's fastest supercomputer for open science [17]. We are especially interested in characterizing GPU soft-errors in the field, focusing on their impact on application performance, their relation to user jobs, GPU resource utilization, and temperature, as well as the relationship between difference kinds of GPU soft-errors. The goal of this chapter is to improve our understanding in the aforementioned aspects and identify observations that are instructive to future system design and resource management.

Unfortunately, there are several challenges in building such an understanding. First, there are often multiple factors responsible for different types of GPU errors, making it hard to distill their cause and their impact on applications. Second, it is hard to study the correlation or impact of applications on GPU reliability characteristics or resource utilization since we do not have access to the end-user application-base. Third, we often do not have control over several factors such the power/cooling conditions, user behavior or node-assignments to different jobs. This makes the development of an accurate understanding of the GPU errors more challenging. Despite these challenges, in this chapter,

we attempt to improve our current understanding about GPU reliability at-scale while carefully considering these challenges.