# **W&M ScholarWorks**

Dissertations, Theses, and Masters Projects

Theses, Dissertations, & Master Projects

2021

# **Exploring Heterogeneous Architectures With Tools And Applications**

Du Shen William & Mary - Arts & Sciences, shendu.nju@gmail.com

Follow this and additional works at: https://scholarworks.wm.edu/etd

Part of the Computer Sciences Commons

#### **Recommended Citation**

Shen, Du, "Exploring Heterogeneous Architectures With Tools And Applications" (2021). Dissertations, Theses, and Masters Projects. William & Mary. Paper 1616444361. http://dx.doi.org/10.21220/s2-f8gh-0967

This Dissertation is brought to you for free and open access by the Theses, Dissertations, & Master Projects at W&M ScholarWorks. It has been accepted for inclusion in Dissertations, Theses, and Masters Projects by an authorized administrator of W&M ScholarWorks. For more information, please contact scholarworks@wm.edu.

# Exploring Heterogeneous Architectures with Tools and Applications

## Du Shen

Williamsburg, VA, USA

Master of Science, College of William & Mary, 2013

A Dissertation presented to the Graduate Faculty of The College of William & Mary in Candidacy for the Degree of Doctor of Philosophy

Department of Computer Science

College of William & Mary January 2021

## APPROVAL PAGE

This Dissertation is submitted in partial fulfillment of the requirements for the degree of

**Doctor of Philosophy**

Du Shen

Approved by the Committee, January 2021

Co-Chair Xu Liu, Courtesy Assistant Professor, Computer Science

North Carolina State University

Co-Chair

Qun Li, Professor, Computer Science

College of William & Mary

Weizhen Mao

Weizhen Mao, Professor, Computer Science College of William & Mary

Bin Ren, Assistant Professor, Computer Science College of William & Mary

Dr. Ang Li, HPC Group

Pacific Northwest National Laboratory

#### **ABSTRACT**

Heterogeneous architectures, including GPU accelerators and memory subsystems consisting fast/slow components, have become popular due to programming flexibility and energy efficiency. Achieving high performance requires sophisticated tools and applications for heterogeneous architectures because they either lack hardware support for fast memory component, or provide complex programming model, which puts extra burdens on compilers and programmers. However, existing tools either rely on simulators or lack support across different GPU architectures, runtime or driver versions. Thus, they only provide insufficient insights.

In the first project, we develop DataPlacer, a profiling tool to provide guidance for data placement. We characterize a real heterogeneous system, the TI KeyStone II, whose memory system consists of fast and slow component, and the fast memory lacks hardware support. We develop a set of parallel benchmarks to characterize the performance and power efficiency of heterogeneous architectures. DataPlacer analyzes memory access patterns and provides high-level feedback at the source-code level for optimization. We apply the data placement optimization to our benchmarks and evaluate the effectiveness of HM in boosting performance ( $11\times$  speedup) and saving energy (50% reduction in energy consumption).

In the second project, we present CUDAAdvisor, a profiling framework to guide code optimization in modern NVIDIA GPUs. General-purpose GPUs have been widely utilized to accelerate parallel applications. Given a relatively complex programming model and fast architecture evolution, producing efficient GPU code is nontrivial. CUDAAdvisor performs various fine-grained analyses based on the profiling results from GPU kernels, such as memory-level analysis (e.g., reuse distance and memory divergence), control flow analysis (e.g., branch divergence) and code-/data-centric debugging. CUDAAdvisor supports GPU profiling across different CUDA versions and architectures. We demonstrate several case studies that derive significant insights to guide GPU code optimization for performance improvement.

In the third project, we present Presponse, a GPU-based incremental graph processing framework which reduces response latency for large-scale graph queries. We first fill the gap that few incremental graph algorithms have been tailored for GPUs. Then, based on the key observation that graph evolution often follows certain patterns that can be accurately predicted, our framework speculatively conducts preprocessing on the graph during the idle period ahead of real graph update, significantly reducing response time. Experiments show that Presponse can predict over 90% of future graph updates, yielding up to a  $25\times$  speedup in graph query response latency.

# TABLE OF CONTENTS

| Acknowledgments                                | ٧    |

|------------------------------------------------|------|

| Dedication                                     | vi   |

| List of Tables                                 | vii  |

| List of Figures                                | viii |

| 1 Introduction                                 | 2    |

| 1.1 Problem Statements                         | 3    |

| 1.2 Contributions                              | 5    |

| 1.3 Dissertation Organization                  | 6    |

| 2 Characterizing Emerging Heterogeneous Memory | 7    |

| 2.1 Introduction                               | 7    |

| 2.2 Related Work                               | 10   |

| 2.3 Testbed Description and Motivation         | 12   |

| 2.4 Design and Implementation of HMBench       | 15   |

| 2.4.1 Benchmark Description                    | 17   |

| 2.4.2 Simple Benchmark Implementation          | 17   |

| Work decomposition                             | 18   |

| Code adaptation for the DSP compiler           | 18   |

| System I/O                                     | 18   |

| Summary: HMBench vs. Rodinia                   | 19   |

| 2.4.3 Limitation of HMBench Implementation     | 19   |

|   | 2.5                                                  | Design and Implementation of DataPlacer                 | 20 |  |  |

|---|------------------------------------------------------|---------------------------------------------------------|----|--|--|

|   |                                                      | 2.5.1 Basic Methodology of DataPlacer                   | 20 |  |  |

|   |                                                      | Tracking array allocations                              | 21 |  |  |

|   |                                                      | Collecting and attributing memory traces                | 21 |  |  |

|   |                                                      | Deriving metrics                                        | 22 |  |  |

|   |                                                      | 2.5.2 Refined Methodology of DataPlacer                 | 22 |  |  |

|   |                                                      | Data locality                                           | 23 |  |  |

|   |                                                      | Large arrays                                            | 23 |  |  |

|   |                                                      | Private vs. shared HM                                   | 24 |  |  |

|   |                                                      | Static vs. dynamic placement                            | 25 |  |  |

|   |                                                      | Hybrid memory subsystem                                 | 27 |  |  |

|   |                                                      | 2.5.3 DataPlacer Output                                 | 27 |  |  |

|   | 2.6                                                  | Evaluation                                              | 29 |  |  |

|   |                                                      | 2.6.1 Optimizing HMBench on KeyStone II                 | 29 |  |  |

|   |                                                      | mtrans                                                  | 30 |  |  |

|   |                                                      | ud                                                      | 30 |  |  |

|   |                                                      | nw                                                      | 30 |  |  |

|   |                                                      | srad                                                    | 31 |  |  |

|   |                                                      | Further analysis on speedups                            | 31 |  |  |

|   |                                                      | 2.6.2 Performance Characterization                      | 32 |  |  |

|   |                                                      | 2.6.3 Power Characterization                            | 35 |  |  |

|   |                                                      | 2.6.4 Takeaways from Experimenting KeyStone II          | 37 |  |  |

|   | 2.7                                                  | Limitations with KeyStone II                            | 37 |  |  |

|   | 2.8                                                  | Chapter Summary                                         | 38 |  |  |

| 3 | СП                                                   | DAAdvisor: LLVM-Based Runtime Profiling for Modern GPUs | 39 |  |  |

| ע | 3.1                                                  | Introduction                                            | 39 |  |  |

|   |                                                      | Existing GPU Profilers and Limitations                  | 42 |  |  |

|   | <b>3.2</b> Existing GPU Profilers and Limitations 42 |                                                         |    |  |  |

|                    | 3.3   | CUDAAdvisor Methodology                                        | 43 |  |

|--------------------|-------|----------------------------------------------------------------|----|--|

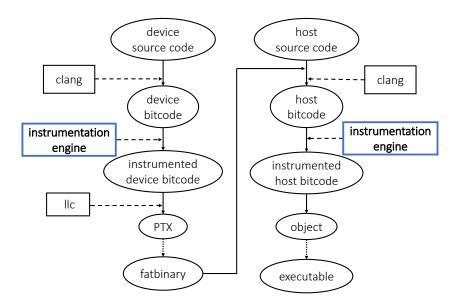

|                    |       | 3.3.1 CUDAAdvisor Instrumentation Engine                       | 44 |  |

|                    |       | (I) Mandatory instrumentation                                  | 44 |  |

|                    |       | (II) Optional instrumentation                                  | 45 |  |

|                    |       | 3.3.2 CUDAAdvisor Profiler                                     | 46 |  |

|                    |       | 3.3.2.1 Code-centric Profiling                                 | 46 |  |

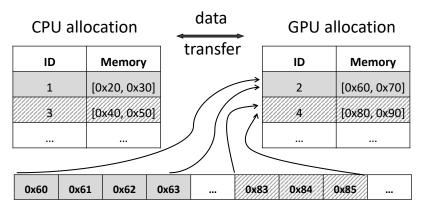

|                    |       | 3.3.2.2 Data-centric Profiling                                 | 47 |  |

|                    |       | 3.3.2.3 Profiling Outputs                                      | 48 |  |

|                    |       | 3.3.3 CUDAAdvisor Analyzer                                     | 48 |  |

|                    |       | 3.3.4 Limitations of CUDAAdvisor                               | 49 |  |

|                    | 3.4   | Evaluation                                                     | 49 |  |

|                    |       | 3.4.1 Evaluation Methodology                                   | 50 |  |

| 3.4.2 Case Studies |       |                                                                |    |  |

|                    | 3.5   | Tool's Overhead Analysis                                       | 64 |  |

|                    | 3.6   | Related Work                                                   | 65 |  |

|                    | 3.7   | Chapter Summary                                                | 66 |  |

| 4                  | Pres  | sponse: Accelerating Incremental Large Graph Processing on GPU |    |  |

|                    | via 🤄 | Speculative Preprocessing                                      | 67 |  |

|                    | 4.1   | Introduction                                                   | 67 |  |

|                    | 4.2   | Background                                                     | 70 |  |

|                    |       | 4.2.1 Graph Embedding                                          | 70 |  |

|                    |       | 4.2.2 GPU Acceleration                                         | 70 |  |

|                    | 4.3   | Methodology                                                    | 71 |  |

|                    |       | 4.3.1 Workflow Overview                                        | 71 |  |

|                    |       | 4.3.2 Presponse Prediction Engine                              | 72 |  |

|                    |       | 4.3.3 Presponse Graph Processing                               | 75 |  |

|                    |       | 4.3.4 Graph Algorithm Implementation                           | 76 |  |

| 4.3.4.1 Breadth First Search (BFS)                           | 76 |

|--------------------------------------------------------------|----|

| 4.3.4.2 Connected Components (CC)                            | 78 |

| 4.3.4.3 Triangle Counting (TC)                               | 79 |

| 4.4 Evaluation                                               | 82 |

| 4.4.1 Experiment Setup                                       | 82 |

| Evaluation Overview                                          | 82 |

| Evaluation Platform                                          | 82 |

| Evaluated Algorithms                                         | 82 |

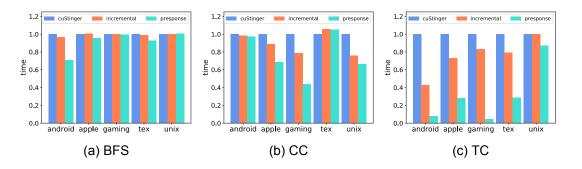

| 4.4.2 Incremental Algorithms                                 | 83 |

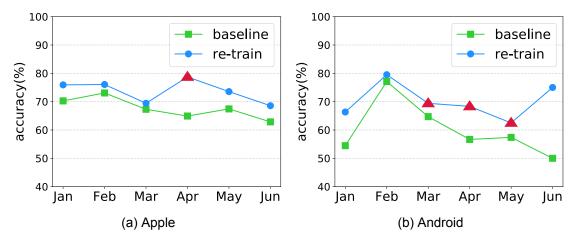

| 4.4.3 Update Batch Prediction                                | 87 |

| 4.4.4 Presponse Performance with Incremental Computation and |    |

| Link Prediction                                              | 88 |

| BFS                                                          | 89 |

| CC                                                           | 90 |

| TC                                                           | 91 |

| 4.5 Related Works                                            | 91 |

| 4.6 Chapter Summary                                          | 94 |

| 5 Conclusion                                                 | 95 |

| Bibliography                                                 | 97 |

#### **ACKNOWLEDGMENTS**

This dissertation is written with the support and help from many individuals. I would like to thank all of them.

First and foremost, I would like to express my deepest appreciation to my advisor and all my committee, Dr. Xu Liu, Professor Qun Li, Professor Weizhen Mao, Dr. Bin Ren and Dr. Ang Li, for serving on my committee as well as providing insightful comments.

I enjoyed working in the office also because of my fellow students: Shasha Wen, Probir Roy, Qingsen Wang, Hao Xu, Pengfei Su, Bolun Li and Jialiang Tan.

In addition, I would like to express my gratitude to my friends here in the 'burg: Mi, Zhen, Han, Shasha, Hongyang. The time we spent together means a lot!

Last but not least, special thanks to Taro for making the world a happier place! Your companionship and comfort helped me through the hard times. Keep on wagging!

| This dissertation is dedicated to my beloved parents, for their endless and |

|-----------------------------------------------------------------------------|

| selfless love and support.                                                  |

|                                                                             |

|                                                                             |

|                                                                             |

|                                                                             |

|                                                                             |

|                                                                             |

vi

# LIST OF TABLES

| 2.1 | Bandwidth comparison of MSMC and DDR with a single thread 1      |    |  |

|-----|------------------------------------------------------------------|----|--|

| 2.2 | Benchmark descriptions.                                          | 16 |  |

| 2.3 | 3 DataPlacer's optimization decisions based on two metrics       |    |  |

| 2.4 | 4 The analysis and optimization guidance provided by DataPlacer. |    |  |

|     | The speedups are measured for all benchmarks running with eight  |    |  |

|     | threads in KeyStone II.                                          | 34 |  |

| 2 1 | GPU architectures for evaluation.                                | 49 |  |

|     |                                                                  |    |  |

| 3.2 | Benchmarks for showcasing CUDAAdvisor.                           | 50 |  |

| 3.3 | Results of Branch Divergence on Pascal                           | 58 |  |

|     |                                                                  |    |  |

| 4.1 | Graph Datasets for Algorithm Evaluations.                        | 83 |  |

| 4.2 | Description of Real-world Datasets.                              | 87 |  |

# LIST OF FIGURES

| 2.1 | The architecture and memory hierarchy of the KeyStone II. Part of   |    |

|-----|---------------------------------------------------------------------|----|

|     | L2 cache in DSP and the whole MSMC shared by DSP and ARM            |    |

|     | are configured as HM by default.                                    | 13 |

| 2.2 | The functionality of DataPlacer. DataPlacer monitors program ex-    |    |

|     | ecution on x86 and generates pure software-based profiles to guide  |    |

|     | program optimization when porting the code to an HM-based ar-       |    |

|     | chitecture.                                                         | 21 |

| 2.3 | Creating a CCT for a program and pruning it by discarding nodes     |    |

|     | with small numbers of memory accesses. The blue nodes are in-       |    |

|     | ternal functions, while the red nodes are leaf functions            | 26 |

| 2.4 | An output example of DataPlacer when monitoring srad                | 28 |

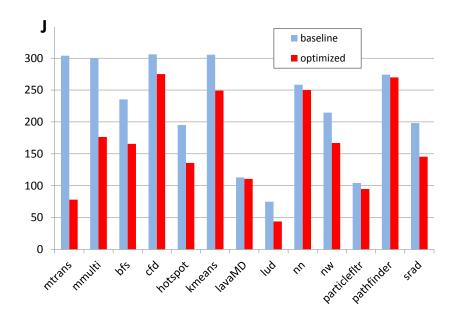

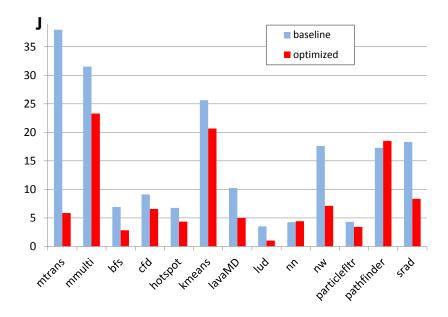

| 2.5 | Comparison of whole-system energy consumption between base-         |    |

|     | line and optimized benchmarks running with eight threads. The       |    |

|     | vertical axis indicates the energy consumption, measured in Joules. | 35 |

| 2.6 | Comparison of dynamic energy consumption between baseline and       |    |

|     | optimized benchmarks running with eight threads. The vertical       |    |

|     | axis indicates the energy consumption, measured in Joules           | 36 |

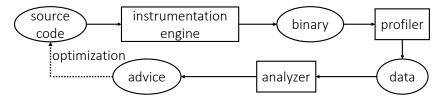

| 3.1 | Workflow of CUDAAdvisor.                                            | 43 |

| 3.2 | The workflow of the engine inserting instrumentation.               | 45 |

| 3.3 | CUDAAdvisor's data-centric profiling.                               | 48 |

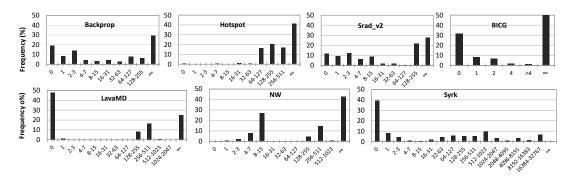

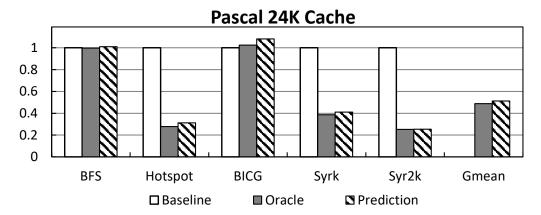

| 3.4  | Reuse distance analysis through CUDAAdvisor. $\infty$ is defined as  |    |

|------|----------------------------------------------------------------------|----|

|      | data is never reused again during the program execution or before    |    |

|      | the next write to the address (e.g., write-evict L1 on NVIDIA GPUs). | 53 |

| 3.5  | Profiled memory divergence distribution of unique touched cache      |    |

|      | ines by instructions of an entire application on Kepler. X-axis rep- |    |

|      | resents number of unique cache lines touched (min is one and max     |    |

|      | s 32). (a) Kepler architecture with 128 Byte cache line; (b) NVIDIA  |    |

|      | Tesla P100 (Pascal) with 32 Byte cache line.                         | 56 |

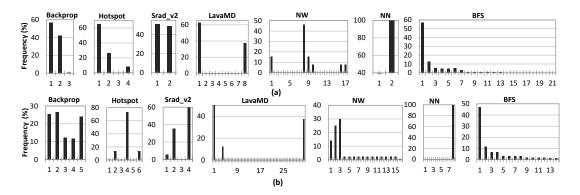

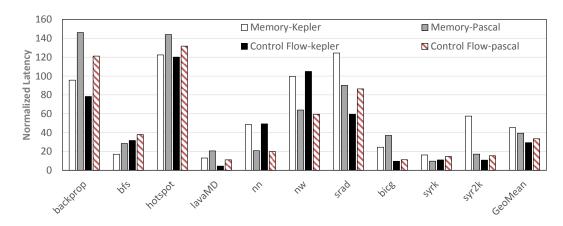

| 3.6  | Normalized execution time of different applications on NVIDIA Ke-    |    |

|      | pler architecture when using the predicted optimal number of warps   |    |

|      | per CTA for bypassing. Baseline case is using all the warps (no by-  |    |

|      | passing). Oracle exhaustively searches the optimal solution. Pre-    |    |

|      | diction represents our model.                                        | 59 |

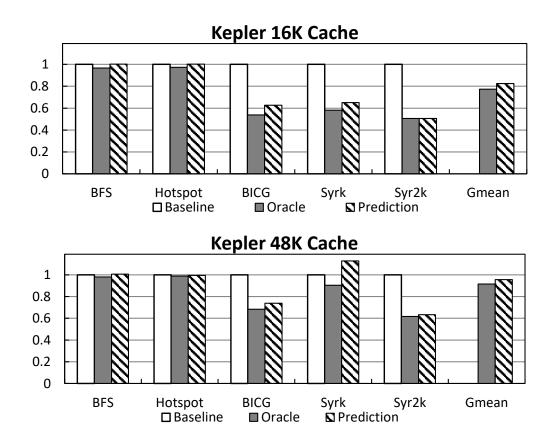

| 3.7  | Normalized execution time of different applications on NVIDIA Pas-   |    |

|      | cal architecture when using the predicted optimal number of warps    |    |

|      | per CTA for bypassing. Baseline case is using all the warps (no by-  |    |

|      | passing). Oracle exhaustively searches the optimal solution. Pre-    |    |

|      | diction represents our model.                                        | 60 |

| 3.8  | Code-centric view shows concatenated calling context from both       |    |

|      | host and device.                                                     | 63 |

| 3.9  | Data-centric view shows the interesting data objects, where it is    |    |

|      | allocated on host and device and where it is transferred             | 64 |

| 3.10 | Overhead of memory and control flow instrumentation, on Kepler       |    |

|      | and Pascal Architectures.                                            | 64 |

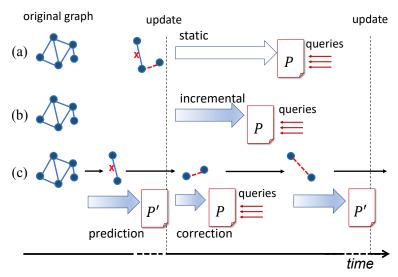

| 4.1 | Comparison of three approaches to evolving graph: (a) static re-    |    |

|-----|---------------------------------------------------------------------|----|

|     | computation, (b) incremental processing, (c) proposed approach.     |    |

|     | The horizontal bottom arrow indicates time. The vertical dashed     |    |

|     | ines indicate batch emit times. The length of blue arrows indicate  |    |

|     | the processing time.                                                | 68 |

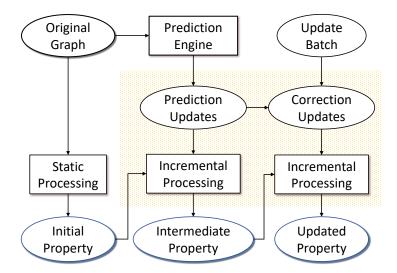

| 4.2 | Workflow of Presponse. The rectangles represents components of      |    |

|     | Presponse. Given the original graph, static processing obtains ini- |    |

|     | tial property and prediction engine generates prediction updates.   |    |

|     | Incremental processing takes updates as input and computes in-      |    |

|     | termediate properties. When an update batch is emitted, incre-      |    |

|     | mental processing takes correction as input and computes up-        |    |

|     | dated property. Orange shaded area represents procedures which      |    |

|     | run repeatedly for each batch.                                      | 72 |

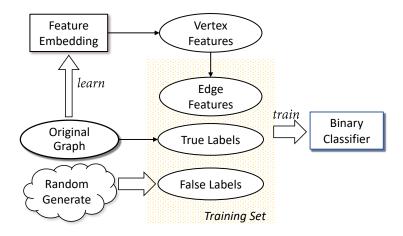

| 4.3 | Details of training a classifier for Presponse's prediction engine. | 74 |

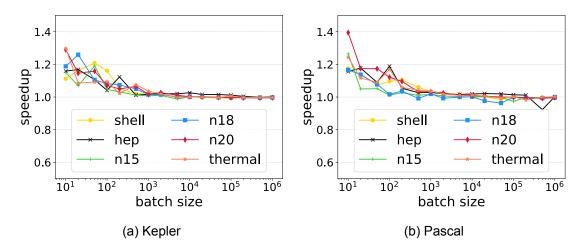

| 4.4 | Speedup of incremental BFS. Horizontal axes are log-scaled. Hor-    |    |

|     | zontal axes represent the size of update batches. Vertical axes     |    |

|     | represent incremental BFS's speedup against static BFS              | 83 |

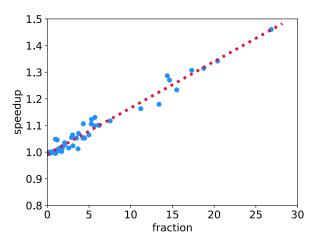

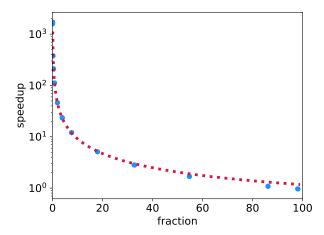

| 4.5 | Relation between speedup and fraction of impacted vertices. The     |    |

|     | horizontal axis represents the fraction of non-impacted vertices in |    |

|     | percentage. The vertical axis represents the ratio of elapsed time  |    |

|     | of incremental BFS computation to static BFS computation. The       |    |

|     | blue scattered points are data points, while the red dashed line    |    |

|     | represents linear fitting.                                          | 84 |

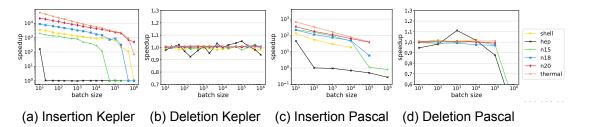

| 4.6 | Speedup of incremental CC. Horizontal axes are log-scaled. For      |    |

|     | deletion cases, both axes are log-scaled. Horizontal axes repre-    |    |

|     | sent the size of update batches. Vertical axes represent incremen-  |    |

|     | tal CC's speedup against static CC.                                 | 84 |

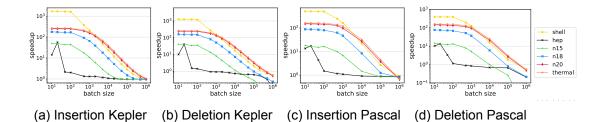

| 4.7  | Speedup of incremental TC. Both axes are log-scaled. Horizontal     |    |

|------|---------------------------------------------------------------------|----|

|      | axes represent the size of update batches. Vertical axes represent  |    |

|      | incremental TC's speedup against static TC.                         | 85 |

| 4.8  | Relation between speedup and fraction of impacted vertices. Hor-    |    |

|      | zontal axis represents the percentage of impacted vertices. Verti-  |    |

|      | cal axis represents speedup. The blue scattered circles represent   |    |

|      | each data point, and the red dashed line represents theoretical     |    |

|      | speedup obtained via regression.                                    | 87 |

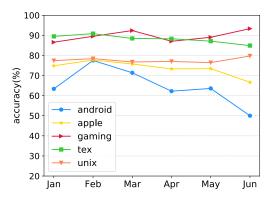

| 4.9  | Prediction accuracy. Horizontal axis represents the time. Vertical  |    |

|      | axis represents prediction accuracy in percentage.                  | 89 |

| 4.10 | Prediction accuracy when re-training enabled. (a) for apple, and    |    |

|      | (b) for android. Horizontal axis represents the time. Vertical axis |    |

|      | represents prediction accuracy, in percentage. Original setup with- |    |

|      | out re-training is shown as baseline. Red triangle markers indicate |    |

|      | points of re-training.                                              | 90 |

Exploring Heterogeneous Architectures with Tools and Applications

# **Chapter 1**

# Introduction

In modern computer systems, emerging parallel architectures offer heterogeneous memory systems to bridge the huge gap between processors and memory. Due to the computation efficiency and programming flexibility, heterogeneous architectures have become increasingly popular and they are widely adopted in computing domains such as accelerating scientific computing applications, deep learning and graph workloads.

A heterogeneous memory system consists of a fast memory component in completion to traditional memory systems. There are various types of heterogeneous architectures, such as Intel Xeon Phi, Texas Instruments KeyStone and Graphics Processing Units (GPUs). Their fast memory component has a higher bandwidth and lower latency. For example, Knights Mill, the latest model of Intel Xeon Phi, has an on-package memory that has  $4\times$  bandwidth as the off-package memory. In addition to that, unlike traditional hardware-managed cache, fast memory component may allow software management where one can control when to hoist or evict data. With this flexibility in programming, one can explicitly control data placement and replacement to further reduce latencies and energy consumption incurred by inappropriate date movement.

However, higher flexibility comes with higher programming requirements. First, heterogeneous architectures require using certain low-level programming models, such as CUDA [1] and OpenCL [2]. Second, without deep insights of the specific architecture, one can suffer from inappropriate usage of the precious resources of fast memory, re-

sulting in higher overhead and energy consumption. For example, the cached data may be evicted without being fully utilized due to an eviction. Similarly for SIMT programming models, such as GPU, control flow divergence or memory divergence can significantly hurt performance. Thus, it is non-trivial to design efficient programs for heterogeneous architectures to fully utilize the computation power.

It is tedious, error-prone and sometimes impossible for large codebases to manually analyzing programs for heterogeneous architectures. Characterizing the performance and energy consumption is important to aid programmers to pinpoint performance bottlenecks. Existing tools like profilers may only provide coarse-grained analysis and the output can barely be helpful to aid programmers directly. On the other hand, simulators and emulators usually incur undesirable overhead and have a limited support for emerging hardware features. Therefore, sophisticated profiling tools and tailored applications are in demanded to achieve high performance on heterogeneous architectures. Thus, in this dissertation, we tackles these problems from two aspects: characterizing heterogeneous architectures with aid find-grained profiling tools and designing tailored applications.

## 1.1 Problem Statements

Characterizing heterogeneous memory subsystems. Nowadays, CPU employs multiple levels of caches to bridge the gap between processor and memory. Accessing memory incurs high latency. However, cache is precious resource due to the limited space. Cache is transparent to programmers and provides only hardware control. That being said, one can not explicitly conduct data placement in cache. Alternatively, emerging parallel architectures offer heterogeneous memory subsystems to complement hardware-managed caches. A typical heterogeneous memory subsystem consists fast and slow memory component and fast memory requires software management. Therefore, without guidance of a tool, inappropriate data placement and movement can

result in unsatisfactory memory performance. Prior work mainly employs simulators to study the data placement. However, it is difficult to simulate every feature of the complex architecture of heterogeneous memory subsystems. In addition, it is time-consuming to evaluate real parallel applications due to the high overhead of simulation. To tackle these two issues, we study real hardware in this dissertation.

Monitoring program execution and guiding optimization for GPUs. General-purpose GPUs are widely adopted in various application domains, including scientific computing, deep learning and graph workloads. Unlike CPUs, GPUs offer a more complex programming and architectural scenario. Thus, efficiently designing a GPU kernel is difficult. For example, designing a GPU kernel usually requires low-level programming languages, such as CUDA and OpenCL. Since GPUs employs SIMT (Single-Instruction Multiple-Threads) programming model, control flow divergence and memory divergence can hurt performance. Moreover, thousands of threads may compete for the precious cache resources. Prior work relies on simulators or emulators to perform fine-grained analysis of GPU programs. However, simulator and emulators do not support every feature of complex architectures. Some other tools may provide fine-grained analysis but have their limitations in terms of portability and coverage. In order to address all these challenges, we present a framework that provides insight of GPU program, covers the interaction between GPU and GPU, and guides optimization.

Accelerating incremental large graph processing on GPU. Large-scale graphs are pervasive nowadays. Meanwhile, enormous queries on certain graph properties impose increasing restrictions on response latency. This demands huge computation power such that GPU is frequently leveraged and incremental processing is adopted for acceleration. However, adopting GPU and incremental processing does not always provide fast responses. It is desired that we further shrink the graph query latencies. Existing works have focused on CPU or Intel Xeon Phi style architectures. However, GPUs introduces different design principles and performance concerns in the parallel execution. Moreover, existing works do not seek approaches other than optimizing algorithms. To

tackle this, we propose an approach that boosts graph processing via link prediction.

## 1.2 Contributions

Characterizing heterogeneous memory subsystems. We characterize the fast and slow component of heterogeneous memory subsystems and apply data placement optimization and evaluate the effectiveness in boosting performance and saving energy. Specifically, we make three contributions.

- We develop a benchmark suite, HMBench. HMBench is coded in OpenMP and runs on heterogeneous memory architectures. To the best of our knowledge, it is the first benchmark suite based on OpenMP 4.0 standard.

- We design a performance tool, DataPlacer, to guide data placement in heterogeneous memory. DataPlacer guides programmers to port their code to a heterogeneous memory system and provides rich information to intuitively present the analysis results.

- We optimize HMBench guided by DataPlacer. We use optimized benchmarks to characterize and understand the importance of HM in both performance and energy.

**Monitoring program execution and guiding optimization for GPUs.** We present a framework that provides insight and guide optimization for GPU program. Specifically, we make three contributions.

- CUDAAdvisor is the first fine-grained GPU profiler that supports various generations of modern NVIDIA GPU architectures and CUDA versions, to the best of our knowledge.

- CUDAAdvisor combines the code- and data-centric profiling results from both CPU and GPU, and associates performance bottlenecks with their root causes.

We demonstrate CUDAAdvisor is able to combine different analyses and derive useful metrics and insights to guide optimizations for GPUs.

Accelerating Incremental Large Graph Processing on GPU. We develop a framework that employs link prediction to boost incremental graph process to reduce graph property query latencies. Specifically, we make four contributions.

- We develop incremental implementations of three fundamental graph algorithms,

Breadth First Search, Connected Components, and Triangle Counting. The implementations are tailored for GPU execution.

- We demonstrate that updates are highly predictable for real-world evolving graphs,

which can greatly benefit the incremental computation.

- We propose Presponse, a framework that leverages graph update prediction and utilizes GPU to boost incremental graph processing.

- We show that Presponse can accelerate important graph algorithms on real-world graphs with significant speedups.

# 1.3 Dissertation Organization

The rest of this dissertation is structured as follows. In Chapter 2, we present our study of characterizing a heterogeneous memory system and guiding data placement. In Chapter 3, we present our tool that monitors program execution and guides code optimization for GPUs. In Chapter 4, we present our framework that reduces graph response latency via link prediction and incremental processing. In Chapter 5, we conclude the dissertation.

# **Chapter 2**

# Characterizing Emerging Heterogeneous Memory

## 2.1 Introduction

In modern computer systems, the speed gap between processors and memory has become huge. As a result, accessing main memory incurs not only high latency but also excessive energy. To bridge such a speed gap, CPUs employ multiple levels of caches. Cache hits reduce memory access latency. Caches are precious resources due to their limited space. For a traditional memory subsystem, hardware manages caches at the granularity of cache lines. Hardware also employs built-in algorithms, e.g., least recently used (LRU), to determine which lines of data to evict. Moreover, multi-core systems employ sophisticated protocols (e.g., MESI) to guarantee the data consistency in private and shared caches, associated with different cores and sockets.

Caches are transparent to compilers and programmers. One cannot explicitly control the data placement and replacement in caches. Software usually cannot explicitly control the data locality to exploit caches. One policy does not fit all usage patterns. Hence, existing hardware-managed caches do not provide a straightforward way to achieve the optimal performance. Without the entire program profile, hardware is handicapped in making best data movement decisions. The situation is aggravated in the context of

parallel architectures, where cores compete for shared cache. For example, the cached data may be evicted without being fully utilized due to an eviction caused by another core. Contention can significantly degrade program performance. Because of the existing hardware-managed cache system, one can only use some workarounds to explicitly but indirectly interact with caches, such as non-temporal instructions [3], cache partitioning based on page coloring [4], and memory footprint reduction via loop tiling [5]. Though effective, these workarounds rely on special support from instruction set architectures (ISAs), special hardware, customized operating systems and complex source code transformations.

As an alternative, emerging parallel architectures offer heterogeneous memory (HM, also known as hybrid memory) to complement hardware-managed caches. A typical HM system consists of a fast memory component and a slow memory component. The fast component, unlike traditional caches, needs explicit software operations to hoist or evict data in or out. Memory techniques include 3D stack memory [ $\overline{b}$ ] and non-volatile memory [ $\overline{b}$ ], which together with traditional DRAM form the emerging HM systems. For example, the latest generation of Intel Xeon Phi, Knights Landing (KNL), has on/off-package memories. The on-package memory has  $5\times$  the bandwidth of off-package memory [ $\overline{b}$ ]. The KNL's memory hierarchy is a kind of HM. Moreover, scratchpad memory [ $\overline{b}$ ] is widely used in accelerators, such as GPUs and digital signal processors (DSPs), and has a higher bandwidth and lower latency than DRAM. *In this chapter, we refer to a system with fast and slow memory as HM*.

HM offers flexibility in managing data. For example, programmers can partition the fast memory across different threads to avoid contention. Another advantage of HM is its power efficiency. HM does not require power hungry hardware mechanisms for cache management [10]. In the foreseeable future, HM will become more popular to complement hardware caches for its programming flexibility.

However, software-based data movement can incur much higher overhead than a hardware-based approach. Thus, inappropriate data placement and frequent data

movement in HM can significantly degrade memory performance, negating its benefit. Therefore, it is important to characterize the performance and energy consumption of HM to achieve beneficial data placement. Prior work mainly utilizes simulators to study the data placement [11], 12, 13, 14, 15]. There are two weaknesses to this approach: first, given the complex architectures, it is difficult to simulate every feature of HM and its interactions with the CPUs. Second, due to the high overhead of simulation, it is time consuming to evaluate real, long-run parallel programs. To address these two issues, we study HM in real hardware in this chapter.

Given the real hardware evaluation, we have the following questions: (1) For a real parallel program, how should we place its data in HM to achieve high performance? (2) How much can a real HM affect a program's performance and energy? In pursuit of answers to these questions, we make three contributions in this chapter:

- We develop a benchmark suite, HMBench. HMBench is coded in OpenMP and runs on HM-based machines. To the best of our knowledge, it is the first benchmark suite based on OpenMP 4.0 standard for studying the performance and energy impacts of HM.

- We design a performance tool, DataPlacer, to guide data placement in HM. This

tool can help programmers when they try to port their code to a system with HM.

DataPlacer provides rich information sorted by key metrics to intuitively present

the analysis results.

- We optimize HMBench guided by DataPlacer. We utilize the original and optimized benchmarks to characterize the capabilities of HM-based architectures and understand the importance of HM in both performance and energy.

We use KeyStone II [10], a server-class ARM+DSP heterogeneous architecture from Texas Instruments, in our studies. KeyStone II's HM consists of an off-chip DRAM and a relatively large on-chip SRAM (scratchpad memory). We choose DRAM+scratchpad memory to study HM because stacked memory and non-volatile memory are not com-

mercially available. Moreover, the scratchpad memory on KeyStone II is much larger than the ones in existing embedded systems, which can be effectively used to emulate the emerging fast memory. In the rest of this chapter, we refer to DRAM and scratchpad memory as HM on KeyStone II.

Our experiments show that HM demands extensive attentions to obtain high performance and low energy benefits. Our DataPlacer provides rich information with reasonable overhead to successfully guide data placement in HM. This chapter also provides insights and practical evaluation of the KeyStone II.

This chapter is organized as follows. Section 2.2 reviews state-of-the-art work and distinguishes our approach from prior work. Section 2.3 describes KeyStone II, the testbed we use to evaluate HM. Section 2.4 describes the design and implementation of HMBench, which is used to characterize the performance and energy effects of HM. Section 2.5 describers DataPlacer, a tool to provide high-level guidance for optimization with HM. Section 2.6 studies HMBench in KeyStone II, including performance characterization, power measurement, and HM-based optimization. Section 2.7 discusses some limitations in studying HM with KeyStone II. Section 4.6 offers our conclusions and previews future work.

## 2.2 Related Work

HM has been recognized as a key alternative or complement to caches and main memory [9]. Due to its simpler hardware design, it can provide high performance, predictability, and energy efficiency. Prior research demonstrates that HM-based systems are able to achieve higher performance than cache-based systems when the program data is carefully placed [16]. In modern accelerators, such as Keystone II[17], HM is regarded as a key enabler for high Gflops/Watt value [18], as has been demonstrated in hand-optimized programs [19]. However, using HM faces key challenges of programmability in obtaining good performance.

Recognizing the significance of HM, much work has been done to ease its management. Unfortunately, due to the difficulty in accessing real hardware platforms and applications, prior evaluation methodologies were limited to two categories: most of them are simulation without actual hardware [20, 21, 22]; some of them replay memory trace on hardware platforms, for which the memory trace is often recorded by using a simulator or software instrumentation [23]. Our efforts bridge the gap with a realistic benchmark suite targeting physical platforms.

The lack of an HM benchmark suite has been an important drawback. In much of the prior work, micro benchmarks have been used [16, 24, 25]. However, it is often difficult to map the micro benchmark outcome to that of real applications. Some work employs macro benchmarks in studying HM, however, with somewhat ad-hoc choices. The macro benchmarks employed include SPEC2006 [20], NAS [26], LULESH [22], or hand-selected apps [21]. It is unclear to what extent these benchmarks can exercise HM and therefore these benchmarks cannot quantify the benefits of HM.

Since HM was often employed in embedded and network processors, embedded systems benchmarks, e.g., MiBench, are often selected in evaluating HM proposals targeting these processors [23, 27]. However, embedded system benchmarks often feature very small working sets, from tens to hundreds of KBs. This is also the case for GPU. Since HM is a critical feature of GPU, well-known GPU benchmarks, e.g. SHOC[28], are often exploiting HM for performance and are used in evaluating software that manages GPU HM [29, 30]. However, SHOC benchmarks are explicitly tuned towards the small HM (a few hundreds of KB) on GPU. Moreover, the CUDA programming model cannot represent the general multithreading models in mainstream CPU processors. Thus, the resulting programs can hardly exercise the large HM that are emerging in new architectures, such as KeyStone II.

Beyond an effective benchmark suite, there exists no tool to guide the data placement in heterogeneous memory systems. Our previous work on memif [31] provides an efficient way to support data movement between fast and slow memory in KeyStone

II. However, memif is an OS service for data movement, providing no guidance for the data placement to an application developer. A recent work [32] describes a profiler to analyze memory access patterns to guide data placement. However, the profiler does not provide performance insights such as memory footprint metrics in the full calling contexts, which are important to understand the data structure allocations and program phases.

Unlike existing approaches, we developed HMBench, which has three unique advantages. First, HMBench is developed based on a widely used benchmark suite, Rodinia, which represents the program behaviors of different domains. Second, HMBench leverages the latest OpenMP 4.0 standard. Furthermore, we developed DataPlacer and released it along with HMBench. DataPlacer, to the best of our knowledge, is the first practical tool that provides high-level optimization guidance, such as a variety of metrics within the full calling contexts, when programmers port source code to a HM-based machine.

# 2.3 Testbed Description and Motivation

Texas Instruments (TI) Corporation developed KeyStone II, a heterogeneous chip that employs CPUs and DSPs. It aims to achieve high performance with low energy costs. A KeyStone II chip integrates a quad-core ARM Cortex-A15 processor as the host CPU and eight TMS320C66x DSPs as accelerators. Each ARM core has 1.4 GHz clock frequency, while each DSP has 1.2 GHz. The theoretical peak performance of the overall chip is 63 GFLOPS of double precision and 198 GFLOPS of single precision [17]. The ARM cores and DSPs are coupled with security and packet processing and Ethernet switching, which is designed for lower energy consumption, compared to multi-chip solutions. The programming models that KeyStone II supports are OpenMP [33] and OpenCL [34]. The design of KeyStone II is for embedded infrastructure applications, such as media processing, high-performance computing, transcoding, security, gam-

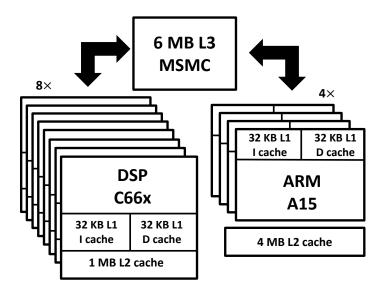

**Figure 2.1**: The architecture and memory hierarchy of the KeyStone II. Part of L2 cache in DSP and the whole MSMC shared by DSP and ARM are configured as HM by default.

ing, analytics, and virtual desktop.

Figure 2.1 shows the architecture of KeyStone II and its memory hierarchy. On the host side, each ARM core has a 32 KB L1 instruction cache and 32 KB data cache. All four ARM cores share a 4 MB L2 cache. Both L1 and L2 caches on the host ARM cores are managed by hardware. On the accelerator side, each DSP has a 64 KB L1 cache and a 1 MB L2 cache. By default, the L2 cache is configured as a 256 KB hardware-managed cache and a 768 KB scratchpad memory. The host and accelerators share a Multicore Shared Memory Controller (MSMC), a scratchpad memory of 6 MB. Beyond MSMC, both CPU and DSP have memory controllers to access main memory (DDR). In KeyStone II, both the scratchpad memory in L2 and MSMC are fast HM layers, which requires software to control the data placement and manage data consistency.

With the default configuration, the KeyStone II has three HM layers: L2 scratchpad memory, L3 MSMC, and DDR. Unlike other embedded systems, the scratchpad memories (L2 and L3) in the KeyStone II are large enough to emulate future HM in the mainstream CPU architectures. To explicitly place the data in each layer, TI provides APIs as shown in Listing 2.1. These APIs, like standard data allocation functions (malloc and

```

1

/* to allocate in L2 */

2

void __heap_init_12 (void *ptr, int size);

/* to manage a heap on L2 */

void *__malloc_12 (size_t size);

/* to allocate in msmc */

7

void __heap_init_msmc (void *ptr, int size);

8 /* to manage a heap on MSMC */

void *__malloc_msmc (size_t size);

void *__calloc_msmc (size_t num, size_t size);

10

void *__realloc_msmc (void *ptr,size_t size);

11

void __free_msmc (void *ptr);

13

void *__memalign_msmc (size_t alignment, size_t size);

14

15 /* to allocate in ddr */

16  void __heap_init_ddr(void *ptr, int size);

17 /* to manage a heap on DDR */

void *__malloc_ddr (size_t size);

19  void *__calloc_ddr (size_t num, size_t size);

void *__realloc_ddr (void *ptr, size_t size);

void __free_ddr (void *ptr);

21

void *_memalign_ddr (size_t alignment, size_t size);

```

Listing 2.1: APIs for managing KeyStone II's L2 cache, MSMC, and DDR. free) in libc, can allocate and free memory in different HM layers. The KeyStone II maps the space of different HM layers to disjoint memory segments. One can simply issue a memory to copy data from one memory segment to another.

#### Performance characterization of the KeyStone II's HM

To evaluate the impacts of L2, MSMC, and DDR in program performance, we developed two micro benchmarks to characterize KeyStone II: Stream and Lat. The description of the two micro benchmarks is as follows:

- Stream, a well-known benchmark [35], is used to quantify the memory bandwidth. It issues memory accesses with streaming patterns, such as array copy, scale, add, and triad. We adapt Stream to measure the bandwidth of both MSMC and DDR.

- Lat is developed for evaluating the performance impact of different data placement policies in HM-based memory hierarchies. The kernel of Lat is a sequence of random accesses to an array placed in a specific HM layer. It also moves data

**Table 2.1**: Bandwidth comparison of MSMC and DDR with a single thread.

| НМ   | сору     | scale    | add      | triad    |

|------|----------|----------|----------|----------|

| MSMC | 5.1 GB/s | 4.8 GB/s | 5.4 GB/s | 5.3 GB/s |

| DDR  | 2.7 GB/s | 2.8 GB/s | 2.6 GB/s | 2.8 GB/s |

between different HM layers to evaluate the data movement latency.

Table 2.1 shows the experimental results of bandwidth tests in MSMC and DDR. We can see that MSMC's bandwidth is around 1.7-2× DDR's bandwidth, with respect to different access patterns. Moreover, Lat shows that placing data in MSMC obtains an 8× acceleration compared to placing data in DDR. The L2 scratchpad memory shows similar latency as MSMC. Additionally, Lat evaluates aggressive data movement policy, which always loads each word one by one from DDR to MSMC before using it. This policy significantly degrades the performance because of the nontrivial overhead incurred by the software-based memory movement. It causes a 10× slowdown compared to the original code with all accesses to DDR, and an 80× slowdown compared to the optimal code with all accesses to MSMC.

The experiments on these two micro benchmarks demonstrate the importance of data placement and data movement policies when porting code to HM-based systems. It is necessary to have a set of benchmarks and tools to characterize the performance impact of HM in the real world. The following sections describe the design and implementation of the benchmarks and tools with this purpose. It is worth noting that the benchmarks we propose in this chapter are general for HM systems beyond the Key-Stone II. It is publicly available at <a href="https://bitbucket.org/hmbench/hmbench.git">https://bitbucket.org/hmbench/hmbench.git</a>.

# 2.4 Design and Implementation of HMBench

We develop HMBench, a benchmark suite to characterize the performance impact of HM in real hardware. HMBench meets the following four criteria.

1. HMBench needs to work on heterogeneous architectures, i.e., CPU+accelerators,

Table 2.2: Benchmark descriptions.

| Application        | Domain                          | Description                                                                                                                                                                                                                         |

|--------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| mtrans             | linear algebra                  | Matrix Transposition.                                                                                                                                                                                                               |

| mmulti             | linear algebra                  | Matrix Multiplication.                                                                                                                                                                                                              |

| bfs                | graph algorithm                 | Breadth-First Search one a graph.                                                                                                                                                                                                   |

| cfd                | fluid dynamics                  | Computational Fluid Dynamics solves 3-                                                                                                                                                                                              |

|                    |                                 | D Euler equations for compression fluid                                                                                                                                                                                             |

|                    |                                 | flow.                                                                                                                                                                                                                               |

| hotspot            | physics simulation              | Hotspot is a thermal simulation bench-                                                                                                                                                                                              |

|                    |                                 | mark that assesses processor tempera-                                                                                                                                                                                               |

|                    |                                 | tures.                                                                                                                                                                                                                              |

| kmeans             | data mining                     | K-means clusters points into user spec-                                                                                                                                                                                             |

|                    |                                 | ified number of categories based on the                                                                                                                                                                                             |

|                    |                                 | distance to other points.                                                                                                                                                                                                           |

| lavaMD             | molecular dynamics              | LavaMD computes particle potentials and                                                                                                                                                                                             |

|                    |                                 | relocation forces. It divides a 3D space                                                                                                                                                                                            |

|                    |                                 | into cubes for computation.                                                                                                                                                                                                         |

| lud                | linear algebra                  | Lud performs matrix LU decomposition.                                                                                                                                                                                               |

| nn                 | data mining                     | Nearest Neighbor is a benchmark that                                                                                                                                                                                                |

|                    |                                 | finds the first k nearest neighbors for a                                                                                                                                                                                           |

|                    |                                 | specified location.                                                                                                                                                                                                                 |

| nw                 | bioinformatics                  | Needleman-Wunsch is a benchmark that                                                                                                                                                                                                |

|                    |                                 | performs DNA sequence alignment opti-                                                                                                                                                                                               |

|                    | modical imaging                 | mization.                                                                                                                                                                                                                           |

| particlefilter     | medical imaging                 | Particle Filter assesses the location of a                                                                                                                                                                                          |

|                    |                                 | target object with noisy measurements of                                                                                                                                                                                            |

| no+hfindor         | arid traversal                  |                                                                                                                                                                                                                                     |

| patiiriider        | grid traversar                  | <u>-</u>                                                                                                                                                                                                                            |

| grad               | image processing                | , , ,                                                                                                                                                                                                                               |

| STau               | inage processing                | · ·                                                                                                                                                                                                                                 |

|                    |                                 |                                                                                                                                                                                                                                     |

|                    |                                 |                                                                                                                                                                                                                                     |

| pathfinder<br>srad | grid traversal image processing | the target's location.  Pathfinder searches a path with the lowest aggregate weights in a 2-D grid.  Srad, with the full name Speckle Reducing Anisotropic Diffusion, is a diffusion algorithm that removes speckles from an image. |

because modern HM (e.g., scratchpad memory + DRAM) is widely used in accelerators, rather than mainstream CPUs.

- HMBench should run in parallel, as accelerators typically employ multiple threads for high thread-level parallelism, which leads to significantly different behaviors in HM from sequential execution.

- 3. HMBench should leverage the interfaces provided by the HM to control the data

placement and movement for evaluating different strategies.

4. HMBench should cover different kinds of applications. As the performance of HM is tightly related to memory access patterns, which differ significantly in different kinds of applications, ranging from data analytics to scientific computing. Thus, a high coverage of applications can evaluate HM thoroughly.

HMBench leverages omp target to support heterogeneous workloads. Thus, HMBench, with minimal adaptation, works on existing and emerging HM architectures in accelerators or co-processors, such as DSP, GPU and Xeon Phi. Moreover, it provides APIs to encapsulate memory management interfaces provided in HM-based architectures. The initial benchmark suite consists of 13 applications from different areas, including two scientific benchmarks for matrix computation and 11 benchmarks derived from Rodinia 2.2 [36]. The reason we choose to adapt Rodinia benchmarks is that Rodinia has a good coverage of application domains. It has an OpenMP implementation but no HM-aware design, which provides us an opportunity to extend its benchmarks with the OpenMP 4.0 standard and HM-friendly design. HMBench is open to enclose more benchmarks in the future. In the rest of this section, we describe different benchmarks in detail and show our design and implementation specific for HM-based accelerators.

## 2.4.1 Benchmark Description

Table 2.2 shows the descriptions of HMBench benchmarks. They are highly representative in their own fields according to Rodinia's specification [36]. Together with two matrix-based scientific benchmarks, HMBench has good coverage of different domains of real-world parallel applications.

#### 2.4.2 Simple Benchmark Implementation

Porting these benchmarks to an HM-based system, such as the KeyStone II, is nontrivial. The challenges come from its uncommon architecture and system support, which

is different from general-purpose CPUs. Specifically, we need to handle work decomposition between CPU and accelerators, limited compiler support in accelerators, and lack of I/O capability in accelerators. In the rest of this section, we use the KeyStone II to illustrate the challenges and our solutions.

**Work decomposition** To fully leverage the computing resources in the KeyStone II, we need to split the work into the CPU part and the DSP part. We apply a simple work decomposition strategy in HMBench: we offload all OpenMP parallel regions to the DSP device and leave all non-OpenMP regions running on the CPU. As most computation is done in the OpenMP regions, this strategy can expose as much as computation for evaluating the HM on the accelerator (DSP) side.

To allow different vendor-provided compilers work on different code regions, the offload code region must be encapsulated in a subroutine and placed in a separate target source file. Thus, the CPU compiler can produce CPU binary and also cross compile the DSP binary for execution. To encapsulate each OpenMP region, we identify its inputs and outputs, which are all passed as arguments by reference to the new subroutine.

Code adaptation for the DSP compiler The DSP compiler only supports C-like syntax. Thus, the code running on the DSP cannot use C++ features, such as classes, memory allocations, and type conversions. Moreover, moving data between CPU and DSP requires the support from DSP's OpenMP compiler, which explicitly accepts array names and sizes. However, the compiler does not support multi-dimensional arrays well. In order to move multi-dimensional arrays between CPU and DSP, we need to map them to a continuous 1-D memory chunk for processing on DSP, and then map them back to the original layout for processing on CPU. Benchmarks, such as pathfinder, need such code transformations.

**System I/O** Some benchmarks, such as bfs and nn, require input files. Since the DSP software stack in the KeyStone II does not support system I/O, we need to modify the

codes so that the host CPU reads input files and map the data to the DSP for computation. DSPs process the data and move it back to the host for writing to the file system. This simple scheme works for most of our benchmarks. However, there is one exception. Benchmark nn repeatedly reads in 10 entries of a database for processing, until completing the whole database. To avoid frequent data movement between CPU and DSP, we perform the I/O once to read in all the entries in the input database and offload them altogether to DSP for processing.

Summary: HMBench vs. Rodinia Although HMBench shares some common programs with the Rodinia benchmark suite, it overhauls their implementations: (1) HMBench uses OpenMP 4.0 omp target to offload parallel regions to accelerators, where we can use the fast scratchpad memory. We identify the input and output data for omp target pragma to ensure the correctness of the code. Moreover, as aforementioned, we need to transpose the array layout for the data transfer between the host and accelerator. (2) HMBench fuses OpenMP regions to minimize the data transfer overhead between the host CPU and the target accelerator. (3) HMBench is extended to manage allocations of heterogeneous memory.

### 2.4.3 Limitation of HMBench Implementation

Our implementation of HMBench is straightforward, without taking the HM into consideration. By default, the compiler places all data in the slow memory, e.g., DDR of the KeyStone II. Benchmarks with this implementation do not achieve good performance. We need to take advantage of different HM layers to cache data for efficient accesses. However, determining which data to place in the fast HM layers is difficult, so we need a profiling tool to help make decisions. The next section describes DataPlacer for this purpose.

# 2.5 Design and Implementation of DataPlacer

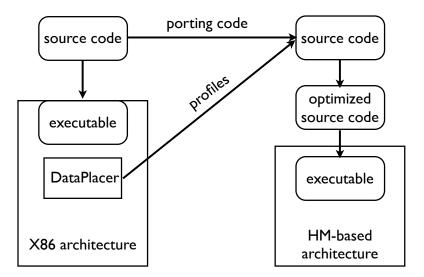

It is challenging for programmers to port code to an HM-based system. One needs high-level guidance to place data objects in the fast HM layers to obtain high performance. In this section, we describe the design and implementation of DataPlacer, a profiler that identifies optimization opportunities of data placement in HM. Figure 2.2 shows the workflow of DataPlacer. DataPlacer works on an x86 host machine. It monitors program execution and provides optimization guidance for porting this code to an HM-based target machine. DataPlacer has the following three features to make it an effective tool.

- DataPlacer provides software metrics only. Because the host and target machines

have different architectures, using the host's hardware metrics is inappropriate to

guide the optimization in the target HM-based machine.

- DataPlacer provides high-level optimization guidance for programmers. The guidance can be easily used for source code transformation.

- DataPlacer can monitor parallel program execution with reasonable overhead. For private and shared HM layers between multi-cores, DataPlacer provides different optimization guidances.

In the rest of this section, we describe the basic methodology of DataPlacer and several refinements to make it practical.

# 2.5.1 Basic Methodology of DataPlacer

DataPlacer leverages Intel Pin [37] to instrument binary and collect memory traces. All the analyses are based on the memory traces without using any information from architecture-specific hardware performance counters. To provide high-level optimization guidance, DataPlacer performs array-centric analysis. It identifies arrays with a significant amount of accesses, which, if put into fast HM layers, can improve performance.

**Figure 2.2**: The functionality of DataPlacer. DataPlacer monitors program execution on x86 and generates pure software-based profiles to guide program optimization when porting the code to an HM-based architecture.

With this guidance, programmers can easily transform the source code for optimization. To achieve array-centric analysis, DataPlacer needs to monitor array allocations, associate memory accesses with arrays, and derive metrics for analysis.

Tracking array allocations DataPlacer leverages Pin to analyze a binary executable and monitor its execution to extract array allocations. DataPlacer monitors both static and heap arrays. On one hand, DataPlacer reads the symbol table of the binary to identify the names and memory ranges of static arrays. On the other hand, DataPlacer instruments array allocation functions, such as malloc, calloc, and realloc, to capture the allocated memory ranges as well as the allocation location mapped to the source code with the help of compiler debugging information. DataPlacer logs these memory ranges and IDs (names for static arrays and allocation sites in source code for heap arrays) into a map for further use.

**Collecting and attributing memory traces** DataPlacer utilizes Pin to instrument both memory loads and stores for their effective addresses. Upon a memory access, Data-Placer checks the map to identify the memory interval that includes the effective address

of this memory access and associates it with the array. DataPlacer counts the number of accesses attributed to each array. For multithreaded programs, accesses from multiple threads can be attributed to the same array at the same time, so DataPlacer needs to use atomic operations to ensure the correctness of accumulating the counter.

**Deriving metrics** From the array-centric analysis, DataPlacer obtains the number of accesses to each array. Arrays with significant accesses are candidates for being placed into the fast HM layers. To weigh the significance of arrays, we use Equation 2.1 to derive a metric  $\hat{F}$  for each array, which is the average access frequency per byte. In the equation, C is the total number of memory accesses to an array. S is the number of memory bytes allocated to the array.

$$\hat{F} = \frac{C}{S} \tag{2.1}$$

DataPlacer sorts all arrays according to  $\hat{F}$ . With a greedy algorithm, DataPlacer recommends placing arrays with high  $\hat{F}$  until the space of HM runs out.

# 2.5.2 Refined Methodology of DataPlacer

The basic design of DataPlacer is inadequate to be used in practice. There are five major issues.

- 1. Metrics  $\hat{F}$  and C alone are insufficient in providing effective guidance. We need more insightful access pattern analysis to extract more features of an array, such locality, beyond the simple access quantity.

- If the fast HM layers have limited space and the arrays used in the programs are too large to fit in, DataPlacer cannot place such large arrays. Moreover, not all elements of an array have the same number of accesses to receive the equal treatment.

- 3. HM may have layers that are private or shared between cores. Applying the same data placing strategy to different kinds of HM layers may hurt performance. For example, inappropriate placement can cause high overhead due to maintaining data consistency.

- 4. DataPlacer produces static data placement guidance. Once the data is loaded into HM, it never gets replaced. In practice, static placement preclude optimal performance because program execution can have different phases with different memory access patterns.

- A system that integrates both traditional hardware caches and HM is difficult to optimize. DataPlacer needs to take this into consideration for HM-based data placement.

Thus, we refine DataPlacer to address all these issues.

**Data locality** An array with a large stride or a random access pattern does not exploit the reuse in caches. We call such array one of poor locality. An array of poor locality can significantly degrade program performance because accesses to this array are more likely to suffer from cache misses and high exposed memory latency. Therefore, DataPlacer prioritizes the placement of arrays with bad locality into fast HM. DataPlacer adopts our previous approach [38] to collect the reuse distance of memory accesses and associates them with arrays. The technology is to instrument all memory accesses and record the trace of effective addresses in a hash map for the computation of reuse distance. We report the instructions and arrays associated with long reuse distances as with poor locality. We evaluate the necessity for placing arrays of poor locality in Section 2.6.

**Large arrays** DataPlacer decomposes the memory intervals allocated for large arrays into small chunks with the sizes not larger than N. N is tunable by programmers; by

default, we set it as one tenth of the HM size. DataPlacer treats each chunk as a separate array and performs original array-centric analysis. With the offsets computed for chunks in the array, programmers can easily place part of the array in the HM. Besides handling large arrays that do not fit into the HM, DataPlacer's array decomposition is more appropriate for handling irregular access patterns. With irregular access patterns, elements in an array may have different access frequencies. The array decomposition provides more details in the array internals for data placement.

Private vs. shared HM HM can be private or shared in a multi-core system, e.g., the KeyStone II. For example, each DSP in the KeyStone II has a private fast layer—L2 cache— and all eight DSPs share a fast layer—L3 MSMC. Optimizations on these two kinds of fast HM layers are different. On one hand, DataPlacer recommends thread-local arrays rather than shared arrays to be placed in private HM because handling shared arrays needs to maintain data consistency. For example, if an element of a shared array is updated by one thread in the private HM, the update should be written back to the main memory. Moreover, all of the copies of this element in different private HMs have to be invalidated and reloaded from the main memory. In a traditional cache system, this data consistency is guaranteed by the hardware, which is efficient. However, HM requires software to keep the data consistency, which is expensive. Thus, DataPlacer avoids recommending shared arrays to be placed in private HM layers.

On the other hand, DataPlacer prioritizes shared arrays to be placed in shared HM layers. If there is space, DataPlacer places local arrays in the shared HM. One strength of this strategy is that no software-based data consistency is needed. Moreover, shared arrays are used by multiple threads, so loading them into shared HM can benefit many threads. In contrast, loading local arrays into shared HM only benefits a subset of threads, rather than all of them.

To provide appropriate optimization guidance, DataPlacer identifies whether an array is local or shared and adapts the array-centric analysis accordingly. When it attributes

memory accesses to arrays, it also associates the IDs of threads that perform the accesses with the array. If an array is accessed by more than one thread, DataPlacer recognizes it as a shared array. Otherwise, it is a local array.

Static vs. dynamic placement The basic implementation of DataPlacer produces the strategies of array placement in a static way: once an array is placed in the HM, it is never evicted throughout the entire execution. However, a typical program has phases. Loading an array into the fast HM layer without using it in some phases can waste the precious HM resources. Therefore, we improve DataPlacer to provide guidance for placing arrays dynamically. The main challenge of generating guidance for dynamic placement is to identify the phase changes to apply dynamic adaptation of data placement. Moreover, DataPlacer needs to provide high-level guidance that can be used by programmers to refactor their source code.

To address the challenge, DataPlacer makes an assumption: phase changes occur at function boundaries. In other words, DataPlacer applies the same data placement strategy inside a function. When switching to a different function, DataPlacer adapts the data placement strategy, if needed, based on the memory accesses in the new function only. However, frequent changes of data placement are costly because of the heavyweight software-based data movements. To reduce the overhead, DataPlacer adapts the data placement when coming into a new function that invokes a significant number of memory accesses. To provide high-level guidance, DataPlacer associates memory accesses with functions in their full calling contexts.

DataPlacer uses Pin [37] to instrument every function call and return instruction. It maintains a shadow stack to track function frames in the system execution stack. When calling a function, DataPlacer pushes the function frame, identified by the starting address of the function, into the shadow stack. When returning from a function, DataPlacer pops the function frame on top of the shadow stack. The calling context of any instruction under execution is in the shadow stack. DataPlacer accumulates the number of

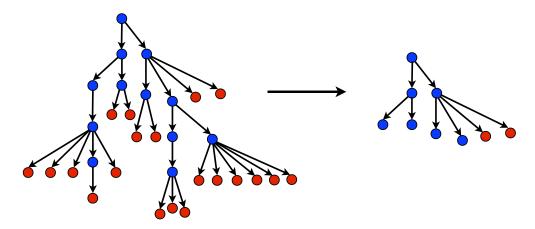

**Figure 2.3**: Creating a CCT for a program and pruning it by discarding nodes with small numbers of memory accesses. The blue nodes are internal functions, while the red nodes are leaf functions.

memory accesses acc to the function frame on top of the shadow stack, as exclusively to the function (not to its callers).